# PEDL22300FFULL-01

Issue Date: Sep. 7, 2007

# OKI Semiconductor ML22310-XXX ML22Q310

# **Preliminary**

**OKI ADPCM Speech Synthesis LSI**

### **GENERAL DESCRIPTION**

The ML22310 and ML22Q310, which include mask ROM and Flash memory for storing speech data, respectively, are speech synthesis LSIs which can controll speech playback utilizing an event input system.

In addition to speech playback, control of peripheral circuits such as LED drive and relay on/off can be provided without using a microcontroller. Speech playback and sequential outputs of 63 patterns specified by the 6-pin event inputs can be performed.

These functions allow easy system configuration by using the logic output from an existing system as the input signals and connecting an external power amplifier.

### **FEATURES**

• Speech system: 4-bit Oki ADPCM2

8-bit/16-bit straight PCM system (can be specified for each phrase)

• Speech ROM capacity

ML22310: 512-Kbit Mask ROM ML22Q310: 512-Kbit Flash (Note 1)

• Sampling frequency: 4.0/8.0/16.0 kHz, 6.4/12.8 kHz, 5.3/10.6 kHz (Note 2)

(fsam can be specified in units of phrase)

• Analog output: Built-in 12-bit DA converter

• Interface: Event input system (built-in noise elimination function)

Sequencer output function: 26 typesMaximum event count: 63 events

• Control mode: Selectable between ML22300 series original control mode and MSM9800

series compatible control mode

• Input pin setting: High-impedance input (CMOS input), pull-down input, or pull-up input is

selectable based on ROM data

• Output pin setting: High-impedance output, CMOS output, Pch open drain output, Nch open

drain output, or LED drive is selectable based on ROM data

Source oscillation frequency: 4.096 MHz (Typ.)

Power supply voltage: 1.8V to 3.6V

• Flash memory rewrite cycles TBD

• Operating temperature range: -40°C to +85°C (ML22310), -20°C to +70°C (ML22Q310)

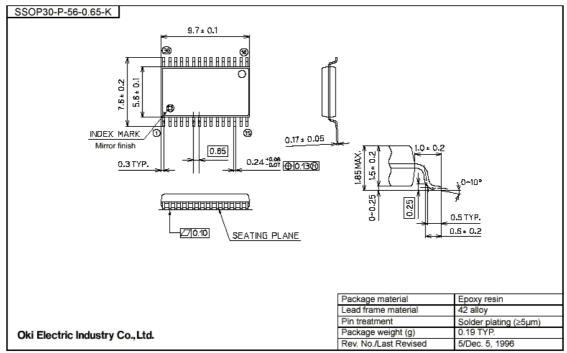

Package: 30-pin plastic SSOP (SSOP30-P-56-0.65-K)

Product name: ML22310-xxxMB (xxx: ROM code number)

ML22Q310MB

Notes: 1) The speech data capacity per phrase should be 512 Kbits or less.

2) When SEQ patterns 17 to 24 and speech synthesis system 4bitOkiADPCM2 are selected, sampling frequencies up to 10.6 kHz must be selected. The sampling frequency of 12.8 kHz or 16 kHz should not be selected.

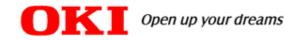

### **BLOCK DIAGRAM**

ML22310-XXX

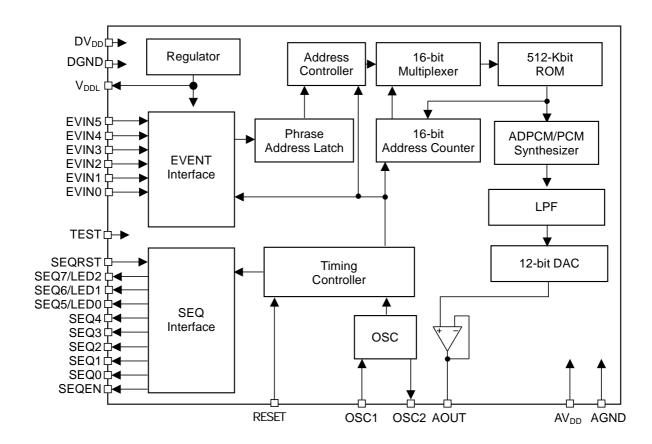

# **BLOCK DIAGRAM**

### ML22Q310

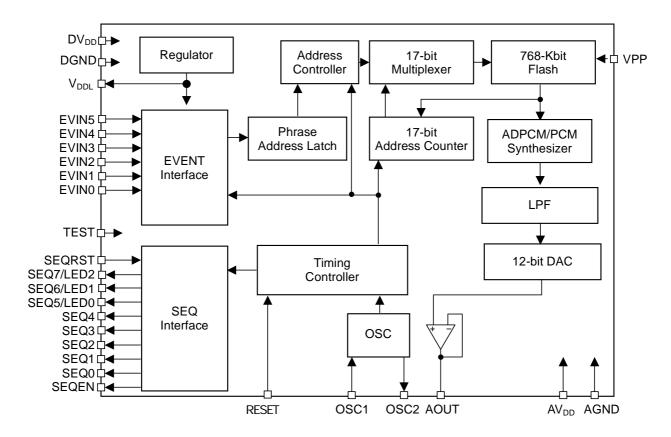

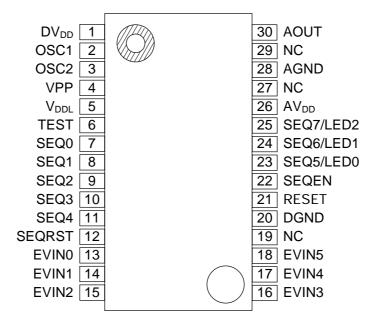

# PIN CONFIGURATION (TOP VIEW)

ML22310-XXX

NC: Unused pin

30-pin Plastic SSOP

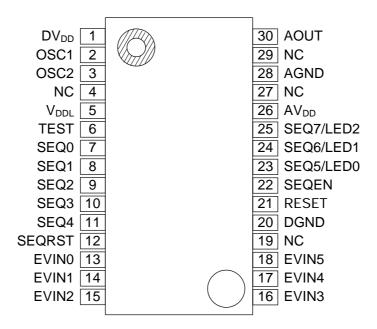

# PIN CONFIGURATION (TOP VIEW)

ML22Q310

NC: Unused pin

30-pin Plastic SSOP

# PIN DESCRIPTIONS

| Pin No.  | symbol                   | I/O  | Description                                                                                                                                           |

|----------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21       | RESET                    | ı    | Place this pin at a "L" level when powered on. After the supply voltage                                                                               |

|          |                          |      | settled, place this pin at a "H" level.                                                                                                               |

| 12       | SEQRST                   | ı    | Sequence reset pin. The speech output and sequence output are stopped in time $t_{CHT}$ after signal change. This output signal is disabled during PC |

| 12       | SEURST                   | ı    | noise elimination.                                                                                                                                    |

|          |                          |      | Event specifying input pins.                                                                                                                          |

| 13       | EVIN0 (SW0)              |      | Event execution or stop can be performed by changes in the input signal                                                                               |

| 14       | EVIN1 (SW1)              |      | to the activation pins set by the EVIN0 pin or ROM option                                                                                             |

| 15       | EVIN2 (SW2)              | _    | Set the unused pins to be pulled up or pulled down.                                                                                                   |

| 16       | EVIN3 (A0)               | I    | When the MSM9800 series control mode is selected, addresses A0 to A                                                                                   |

| 17       | EVIN4 (A1)<br>EVIN5 (A2) |      | after 16 ms are captured by changing the input signals to the SW0 to SW                                                                               |

| 18       | *Note 1                  |      | pins and the speech output is started. The SW0 to SW2 pins are pulled                                                                                 |

|          | Note 1                   |      | down.                                                                                                                                                 |

| 6        | TEST                     | I    | Input pin for testing. Fix this pin at a "L" level (DGND level).                                                                                      |

|          |                          |      | Pin for connecting a crystal or a ceramic vibrator.                                                                                                   |

| 2        | OSC1                     | ı    | A feed back resistor (about 1 M $\Omega$ ) is included between OSC1 and OSC                                                                           |

|          |                          |      | pins.                                                                                                                                                 |

|          |                          |      | When a vibrator is used, place it as close to the LSI as possible.                                                                                    |

| 3        | OSC2                     | 0    | Pin for connecting a crystal or a ceramic vibrator. When a vibrator is used, place it as close to the LSI as possible.                                |

| 7        | SEQ0                     |      | When a vibrator is used, place it as close to the Lor as possible.                                                                                    |

| 8        | SEQ1                     |      |                                                                                                                                                       |

| 9        | SEQ2                     | 0    | Sequencer output pins.                                                                                                                                |

| 10       | SEQ3                     |      | The patterns set by ROM option are output.                                                                                                            |

| 11       | SEQ4                     |      |                                                                                                                                                       |

|          | SEQ5/LED0                |      |                                                                                                                                                       |

| 23       | SEQ6/LED1                | 0    | Sequencer output pins.                                                                                                                                |

| 24<br>25 | SEQ7/LED2<br>(BUSY)      | 0    | The patterns set by ROM option are output. And these pins can be set for the LED drive pins.                                                          |

| 23       | *Note 1                  |      | And these pins can be set for the ELD drive pins.                                                                                                     |

|          |                          |      | Pin for selecting the MSM9800 series control mode or ML22300 series                                                                                   |

|          |                          |      | control mode. When powered on, the MSM9800 series control mode                                                                                        |

| 22       | SEQEN                    | I/O  | selected by placing this pin at a "L" level. When selecting the ML2230                                                                                |

|          | 024211                   | ., 0 | series control mode, place this pin at any level other than the "L" level                                                                             |

|          |                          |      | This output signal is the status output signal during event execution.                                                                                |

| 20       | ACUT                     | 0    | Active "L" or "H" can be selected by ROM option.                                                                                                      |

| 30       | AOUT<br>VPP              | U    | Playback signal output pin.  Power supply pin for rewriting Flash memory.                                                                             |

| 4        | *Note 2                  | _    | Fix this pin to GND except when rewriting Flash memory.                                                                                               |

| 0.5      |                          |      | Analog power supply pin.                                                                                                                              |

| 26       | $AV_{DD}$                | _    | Connect a capacitor of 0.1 µF or more between this pin and AGND.                                                                                      |

| 4        | DV                       |      | Digital power supply pin.                                                                                                                             |

| 1        | $DV_{DD}$                | _    | Connect a capacitor of 0.1 μF or more between this pin and DGND.                                                                                      |

|          |                          |      | Output pin of the regulator for the internal logic power supply.                                                                                      |

| 5        | VDDL                     | _    | Connect a electrolytic capacitor of 10 uF or more and a ceramic capacit                                                                               |

|          |                          |      | of 0.1 μF or more between the VDDL and DGND pins.                                                                                                     |

| 20       | DGND                     |      | Digital ground pin.                                                                                                                                   |

| 28       | AGND                     |      | Analog ground pin.                                                                                                                                    |

# ABSOLUTE MAXIMUM RATINGS

(DGND = AGND = 0 V)

| Parameter                           | Symbol           | Condition                                            | Rating                        | Unit |  |

|-------------------------------------|------------------|------------------------------------------------------|-------------------------------|------|--|

| Digital power supply voltage        | DV <sub>DD</sub> |                                                      | -0.3 to +4.5                  | V    |  |

| Analog power supply voltage         | AV <sub>DD</sub> | Ta = 25 °C                                           | -0.3 to +4.5                  | V    |  |

| Internal logic power supply voltage | $V_{DDL}$        | 1a = 25 C                                            | -0.3 to +3.6                  |      |  |

| Flash power supply voltage (Note 1) | VPP              |                                                      | -0.3 to +10.5                 | V    |  |

| Input voltage                       | V <sub>IN</sub>  | Ta = 25 °C<br>When JEDEC 2-layer<br>board is mounted | -0.3 to DV <sub>DD</sub> +0.3 | V    |  |

| Power dissipation                   | P <sub>D</sub>   | Ta = 25 °C                                           | 790                           | W    |  |

| Output short current                | I <sub>SC</sub>  | 1a = 25 C                                            | 10                            | mA   |  |

| Storage temperature                 | T <sub>STG</sub> | _                                                    | −55 to +150                   | °C   |  |

Note 1: Applies to the ML22Q310.

# RECOMMENDED OPERATING CONDITIONS

(DGND = AGND = 0 V)

| Parameter                    | Symbol           | Condition      | n Ra               |            |      | Unit  |  |

|------------------------------|------------------|----------------|--------------------|------------|------|-------|--|

| Digital newer augusts        |                  | _              |                    | 1.8 to 3.6 |      |       |  |

| Digital power supply voltage | $DV_DD$          | ML22Q310 read  |                    | 1.8 to 3.6 |      | V     |  |

| voltage                      |                  | ML22Q310 write |                    | 3.0 to 3.6 | 6    |       |  |

| Analog power supply voltage  | AV <sub>DD</sub> | _              | 1.8 to 3.6         |            |      | V     |  |

| Flash power supply voltage   | VPP              | ML22Q310 write |                    | 7.7 to 8.3 | V    |       |  |

| Flash memory rewrite cycles  | N                | ML22Q310       |                    | TBD        |      | _     |  |

|                              | T <sub>OP1</sub> | ML22310        | ML22310 -40 to +85 |            |      |       |  |

| Operating temperature        | T <sub>OP2</sub> | ML22Q310 read  | -                  | −20 to +70 |      | °C    |  |

|                              | T <sub>OP3</sub> | ML22Q310 write | 0 to +40           |            |      |       |  |

| Source oscillation           | <b>f</b>         |                | Min.               | Тур.       | Max. | MHz   |  |

| frequency                    | fosc             | _              | 3.5                | 4.096      | 4.5  | IVI⊓Z |  |

# **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

ML22310: DV<sub>DD</sub> = AV<sub>DD</sub> = 1.8 to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C ML22Q310: DV<sub>DD</sub> = AV<sub>DD</sub> = 1.8 to 3.6 V, DGND = AGND = 0 V, Ta = -20 to +70°C

|                                 |                   | $22Q310. DV_{DD} = AV_{DD} = 1.810 3.6$                             |                      |      |                     |      |

|---------------------------------|-------------------|---------------------------------------------------------------------|----------------------|------|---------------------|------|

| Parameter                       | Symbol            | Condition                                                           | Min.                 | Тур. | Max.                | Unit |

| "H" input voltage               | $V_{IH}$          | _                                                                   | $0.8 \times V_{DD}$  | —    | $V_{DD}$            | V    |

| "L" voltage                     | $V_{IL}$          | _                                                                   | 0                    | _    | $0.2 \times V_{DD}$ | V    |

| "H" output voltage 1            | V <sub>OH1</sub>  | $I_{OH} = -0.5 \text{ mA}$ CMOS output, Pch open drain selected     | V <sub>DD</sub> -0.5 |      | _                   | V    |

| "H" output voltage 2            | V <sub>OH2</sub>  | I <sub>OH</sub> = -100 μA<br>OSC2 pin                               | V <sub>DD</sub> -0.5 | _    | _                   | V    |

| "L" output voltage 1            | V <sub>OL1</sub>  | I <sub>OL</sub> = 0.5 mA<br>CMOS output,<br>Nch open drain selected | _                    | ı    | 0.5                 | V    |

| "L" output voltage 2            | V <sub>OL2</sub>  | I <sub>OL</sub> = 100 μA<br>OSC2 pin                                | _                    | ı    | 0.5                 | V    |

| "L" output voltage 3            | V <sub>OL3</sub>  | I <sub>OL</sub> = 5 mA<br>LED mode selected                         | _                    | _    | 0.5                 | V    |

| "H" input current 1             | I <sub>IH1</sub>  | $V_{IH} = DV_{DD}$<br>High-impedance input selected                 | _                    | _    | 1                   | μA   |

| "H" input current 2             | I <sub>IH2</sub>  | $V_{IH} = DV_{DD}$<br>OSC1 pin                                      | 0.3                  | 3    | 15                  | μA   |

| "H" input current 3             | I <sub>IH3</sub>  | $V_{IH} = DV_{DD}$<br>TEST pin                                      | 0.04                 | 0.6  | 3                   | mA   |

| "H" input current 4             | I <sub>IH4</sub>  | $V_{IH} = DV_{DD}$<br>Pull-down input selected                      | 2                    | 30   | 200                 | μA   |

| "L" input current 1             | I <sub>IL1</sub>  | V <sub>IL</sub> = DGND<br>High-impedance input selected             | -1                   | _    |                     | μA   |

| "L" input current 2             | I <sub>IL2</sub>  | V <sub>IL</sub> = DGND<br>OSC1 pin                                  | -15                  | -3   | -0.3                | μA   |

| "L" input current 3             | I <sub>IL3</sub>  | $V_{IL} = DGND$<br>RESET pin                                        | -1.5                 | -0.3 | -0.02               | mA   |

| "L" input current 4             | $I_{1L4}$         | $V_{IH} = DV_{DD}$<br>Pull-up input selected                        | -200                 | -30  | -2                  | μA   |

|                                 | I <sub>DD1</sub>  | f <sub>OSC</sub> = 4.096 MHz<br>Non-loaded output<br>ML22310        | _                    | 3    | 4                   |      |

| Supply current during operation | I <sub>DD2</sub>  | f <sub>OSC</sub> = 4.096 MHz<br>Non-loaded output<br>ML22Q310       | _                    | 6    | 10                  | mA   |

|                                 | I <sub>DD3</sub>  | Flash memory write<br>ML22Q310                                      | _                    | 7    | 15                  |      |

| Supply current during           | I <sub>DDS1</sub> | Ta = -20 to +40°C                                                   | _                    | 1    | 3                   | μA   |

| power down                      | I <sub>DDS2</sub> | Ta = -40 to +85°C                                                   | _                    | 1    | 15                  | μ/ ( |

### **Analog Characteristics**

ML22310: DV<sub>DD</sub> = AV<sub>DD</sub> = 1.8 to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C ML22Q310: DV<sub>DD</sub> = AV<sub>DD</sub> = 1.8 to 3.6 V, DGND = AGND = 0 V, Ta = -20 to +70°C

| Parameter                   | Symbol            | Condition                                                     | Min.                 | Тур. | Max.                 | Unit |

|-----------------------------|-------------------|---------------------------------------------------------------|----------------------|------|----------------------|------|

| AOUT output load resistance | R <sub>LAO</sub>  | Silence playback                                              | 5                    | _    | _                    | kΩ   |

| AOLIT quitaut valtaga ranga | V                 | Non-loaded output $AV_{DD} = 2.1 \text{ V to } 3.6 \text{ V}$ | 0.07×V <sub>DD</sub> | _    | 0.64×V <sub>DD</sub> | V    |

| AOUT output voltage range   | V <sub>AOUT</sub> | Non-loaded output $AV_{DD} = 1.8 \text{ V to } 2.0 \text{ V}$ | 0.07×V <sub>DD</sub> |      | 0.58×V <sub>DD</sub> | V    |

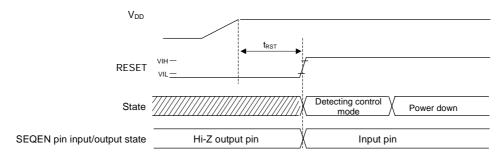

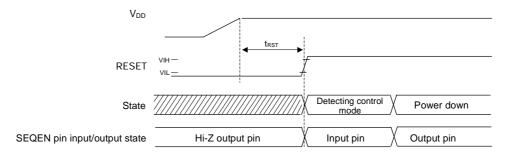

### **AC Characteristics**

ML22310:  $DV_{DD} = AV_{DD} = 1.8$  to 3.6 V, DGND = AGND = 0 V, Ta = -40 to  $+85^{\circ}$ C ML22Q310:  $DV_{DD} = AV_{DD} = 1.8$  to 3.6 V, DGND = AGND = 0 V, Ta = -20 to  $+70^{\circ}$ C

| Parameter                        |                   | Symbol                               | Condition                            | Min. | Typ. | Max. | Unit |

|----------------------------------|-------------------|--------------------------------------|--------------------------------------|------|------|------|------|

| Duty cycle of source oscillation | f <sub>duty</sub> | _                                    | 40                                   | 50   | 60   | %    |      |

| RESET input pulse width          | t <sub>RST</sub>  | t <sub>RST</sub> —                   |                                      | _    | _    | μS   |      |

| SEQRST input pulse width         |                   | t <sub>SEQR</sub>                    | t <sub>SEQR</sub> —                  |      | _    | _    | ms   |

| EVINn input pulse width          |                   | t <sub>EVIN</sub>                    | _                                    | 8    | _    | _    | ms   |

| Initialize time                  |                   | t <sub>INIT</sub>                    | _                                    |      | _    | 2    | ms   |

| Oscillation stabilizing time     |                   | tosc                                 | _                                    | _    | _    | 16   | ms   |

|                                  |                   | t <sub>CHT</sub>                     | _                                    | 6    | _    | 66   | ms   |

| Noise elimination time           | Note 1            | t <sub>CHTA</sub>                    | MSM9800 series control mode selected | 14   | 16   | 18   | ms   |

| Pop noise elimination time       | Note 2            | t <sub>DAR</sub><br>t <sub>DAF</sub> | _                                    | 30   | _    | 258  | ms   |

| Shift-to-standby time            | Note 3            | t <sub>STB</sub>                     | _                                    | 0    | _    | 514  | ms   |

# Notes:

- 1. Select the noise elimination time using the ROM option.

- 2. Select the pop noise elimination time using the ROM option.

- 3. Select the shift-to-standby time using the ROM option.

Load capacitance of the output pins = 55 pF (max.)

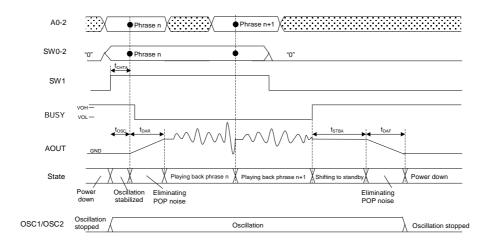

# **TIMING DIAGRAMS**

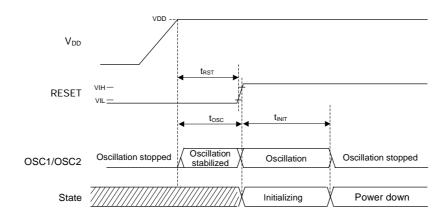

### Power On

When the power is turned on and a reset is released, event execution by the EVIN0 to 5 pin states are started. Set the EVEIN0 to 5 pins to all "0s" when not desired to start the event execution.

# **ML22300 Series Control Modes**

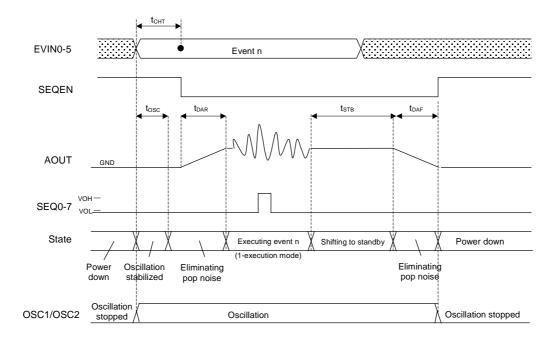

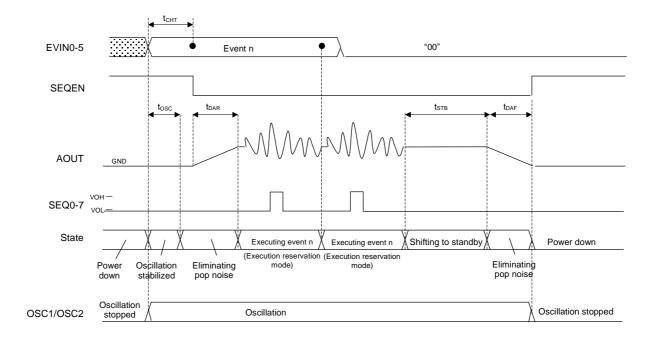

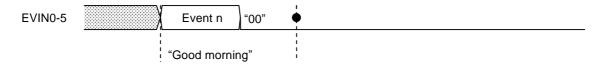

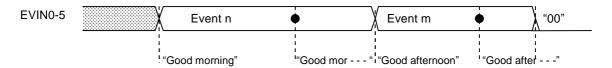

Event Control 1 (Event 1-execution timing diagram in event 1-execution mode)

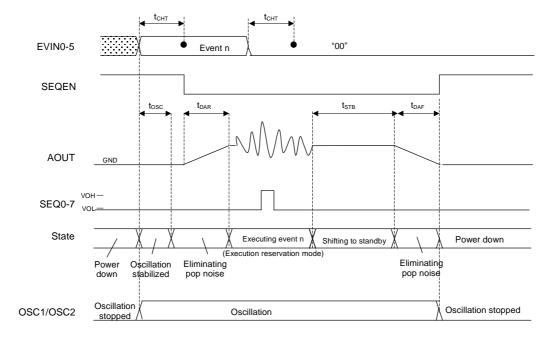

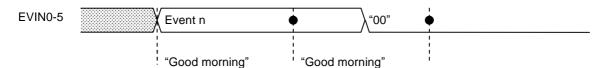

Event Control 2 (Event 1-execution timing diagram in event execution reservation mode)

Event Control 3 (Repetitive event execution timing diagram in event execution reservation mode)

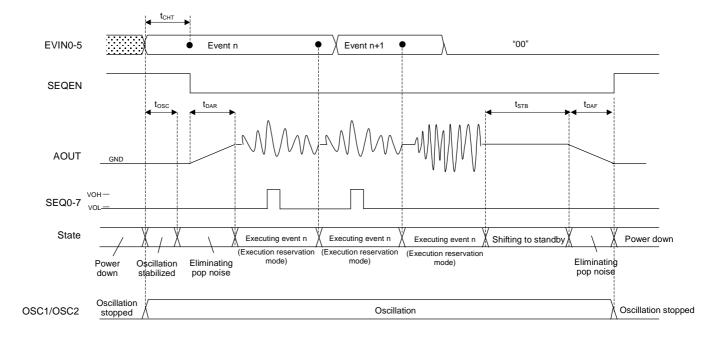

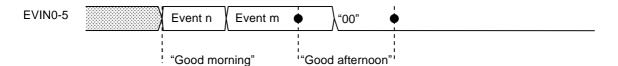

Event Control 4 (Different consecutive event execution timing diagram in event execution reservation mode)

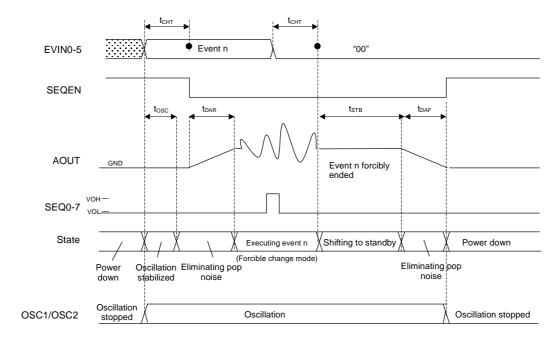

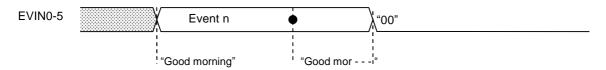

Event Control 5 (Event 1-execution timing diagram in forcible event change mode)

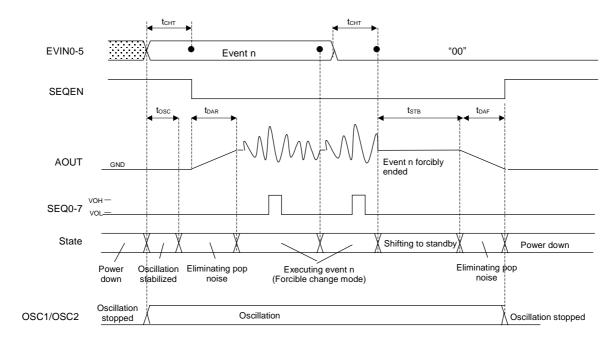

Event Control 6 (Repetitive event execution timing diagram in forcible event change mode)

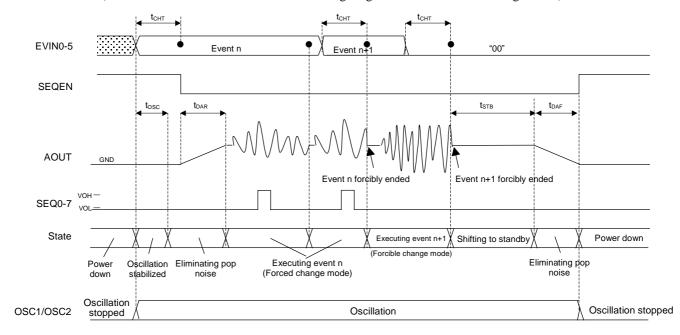

# Event Control 7 (Different consecutive event execution timing diagram in forcible event change mode)

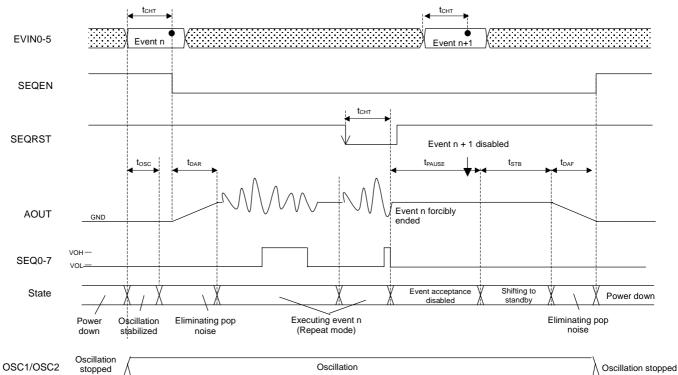

# Event Control 8 (Repetitive event execution timing diagram in event repeat mode)

# **MSM9800 Series Control Modes**

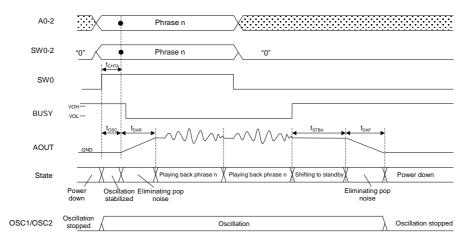

# Repetitive voice reproduction mode

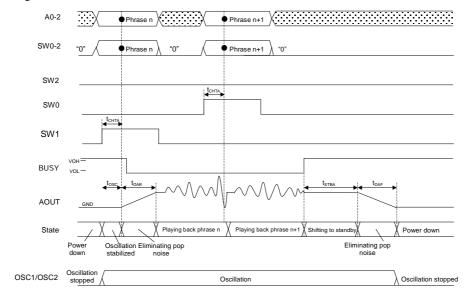

# Forcible change mode

# **Execution Reservation Mode**

### **DESCRIPTION OF FUNCTIONS**

### **Selection of Control Mode**

The MSM9800 series control mode or ML22300 series control mode is selected by setting the SEQEN pin. When SEQEN = 1, the MSM9800 series control mode is selected.

When selecting the ML22300 series control mode, place the SEQEN pin at any level other than a "L" level.

When the MSM9800 series control mode is selected (SEQEN = "L")

When the ML22300 series control mode is selected (SEQEN = other than "L")

### **Initial Setting**

Set the noise elimination time, AOUT output rise/fall time, shift-to-standby time, EVIN0-5 activation pins, EVIN0-to5 pins, SEQ0-7 output sates, SEQ0-7 pins, SEQRST pin signal, and SEQRST pin by using ROM option. Read ROM option data during initialization after powered on and perform each of the above settings.

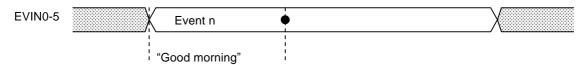

## **Event Activation**

Power-down is released by the change in the input signal to the EVIN0 pin or the activation pin set by ROM option, and the address specified by the EVIN0-5 pins in time tCHT is internally captured and the event execution according to the address is started.

Power-down is released on the rising or falling edge of the input signal to the EVIN0 pin or the activation pin set by ROM option. By changes in the input signals other than the rising or falling edge of the input signal, power-down is not released.

### **Control Method 1 (ML22300 Series Control Mode)**

O Event Control 1 (Only one playback in 1-execution mode)

Only one event specified is executed after event activation. Control method: Input the event address to be executed to the EVIN0-5 pins.

O Event Control 2 (Only one playback in execution reservation mode)

Operation: Only one specification mode is executed

Control method: Input the event address to be executed to the EVIN0-5 pins. After event activation, input "00"

to the EVIN0-5 pins before event execution is ended.

O Event Control 3 (Repetitive playback in execution reservation mode)

Operation: While the EVIN0-5 pin states are held, the event execution is repeated.

In the case of the event execution stop, the event execution is terminated.

Control method: Input the event address to be executed to the EVIN0-5 pins. After event activation, hold the

EVIN0-5 pin states. When desired to stop event execution, input all "0s" to the EVIN0-5

pins.

O Event Control 4 (Change in playback phrase in execution reservation mode)

Operation:

The event execution specified first is ended and newly specified event execution is started. Control method: Input the event address to be executed to the EVIN0-5 pins. After event activation, input the event address to be executed next to the EVINO-5 pins and hold the EVINO-5 pin states until the current event execution is ended.

### O Event Controls 5 and 6 (Repetitive playback in forcible change mode)

Operation: Event execution is performed until the EVIN0-5 pin states are changed. The event execution

stops when the EVIN0-5 pin states are changed.

Input the event address to be executed to the EVINO-5 pins. After event activation, hold the Control method:

EVIN0-5 pin states while the event execution is to be performed. When desired to stop event

execution, input all "0s" to the EVIN0-5 pins

O Event Control 7 (Change in playback phrase in forcible change mode)

Operation:

The event execution specified first is ended and newly specified event execution is started. Control method: Input the event address to be executed to the EVIN0-5 pins. After event activation, input the event address to be executed next to the EVIN0-5 pins

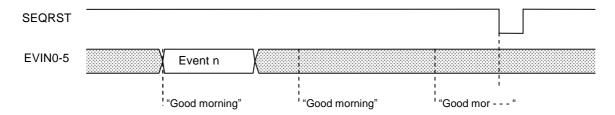

O Event Control 8 (Repetitive playback in repeat mode)

Event execution is repeated until the signal is input to the SEQRST pin. Operation:

Control method: Input the event address to be executed to the EVIN0-5 pins. When desired to stop the event

execution, input a signal to the SEQRST pin. During event execution, the changes in the

EVIN0-5 pin states are disabled.

### Control Method 2 (MSM9800 Series Control Mode)

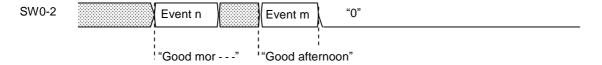

### O Repetitive voice reproduction mode

Operation: Mode reproducing playback phrase as voice repetitively

Control method: Playback is started when the input signals to the SW0-2 pins are changed. Playback is not

changed if the input signals to the A0-2 pins are changed. Place the SW0-2 pins at a "L" level when powered on and reset. When the A0-2 pin and SW0-2 pin states when playback is started are the same as those when playback is ended, this mode is enabled.

SW0-2 Event n • "0" • Good morning" Good morning

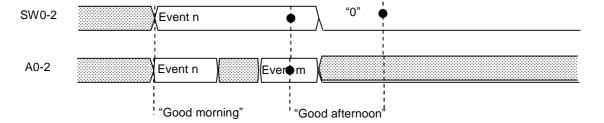

### O Forcible change mode

Operation: Mode in which the current phrase playback is immediately ended and the new phrase is

played back when the input signals to the SW0-2 pins are changed during phrase playback.

Control method: Playback is started when the input signals to the SW0-2 pins are changed. When the input

signals to the SW0-2 pins are changed during phrase playback, the current phrase is ended

and the new phrase is played back.

### O Execution reservation mode

Operation: Event execution specified first is ended and newly specified event execution is started. Control method: Mode in which when the input signals to the SW0-2 pins are changed during phrase playback,

new phrase is played back after the current phrase playback is ended.

When playback is ended, this mode is enabled when the SW0-2 pins are at a "H" level.

### **Sequencer Output**

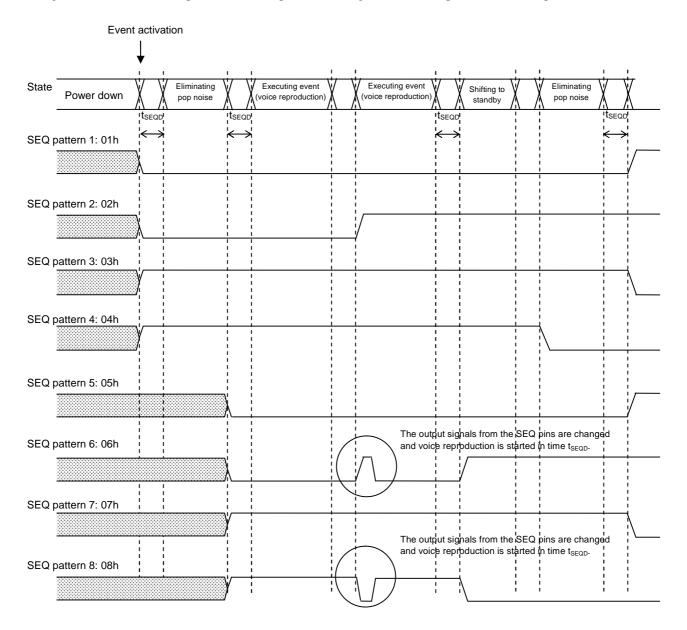

The patterns specified to the SEQ0-7 pins are output by specifying the SEQ patterns shown below in the event management area. When SEQ pattern "00h" is specified, the signals are not output from the SEQ pins.

### SEQ pattern 1: 01h

The "L" level is output after event activation, and POP noise elimination is started in time  $t_{SEQD}$ . The "H" level is output in time  $t_{SEQD}$  after voice reproduction/POP noise elimination processing end.

### SEQ pattern 2: 02h

The "L" level is output after event activation, and POP noise elimination is started in time  $t_{SEQD}$ . The "H" level is output in time  $t_{SEQD}$  after voice reproduction processing end.

### SEQ pattern 3: 03h

The "H" level is output after event activation, and noise elimination is started in time t<sub>SEOD</sub>.

The "L" level is output in time t<sub>SEQD</sub> after voice reproduction/POP noise elimination processing end.

### SEQ pattern 4: 04h

The "H" level is output after event activation, and POP noise elimination is started in time  $t_{SEQD}$ . The "L" level is output in time  $t_{SEQD}$  after voice reproduction processing/shift-to-standby processing end.

### SEQ pattern 5: 05h

The "L" level is output after event activation/POP noise elimination processing end, and voice reproduction processing is started in time  $t_{SEOD}$ .

The "H" level is output in time t<sub>SEQD</sub> after voice reproduction/POP noise elimination processing end.

### SEQ pattern 6: 06h

The "L" level is output time  $t_{SEQD}$  before voice reproduction start, and the "H" level is output in time  $t_{SEQD}$  after voice reproduction end.

# SEQ pattern 7: 07h

The "H" level is output after event activation/POP noise elimination processing end, and voice reproduction processing is started in time  $t_{SEOD}$ .

The "L" level is output in time t<sub>SEQD</sub> after voice reproduction/POP noise elimination processing end.

### SEQ pattern 8: 08h

The "H" level is output  $t_{SEQD}$  before voice reproduction start, and the "L" level is output in time  $t_{SEQD}$  after voice reproduction end.

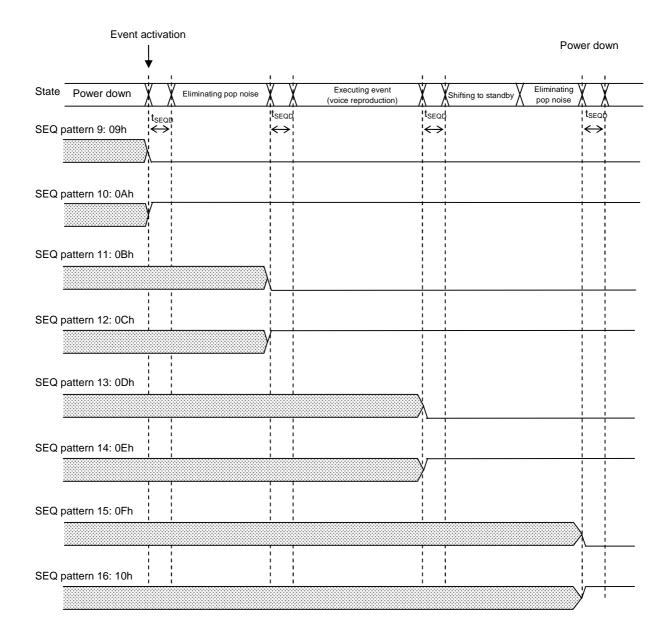

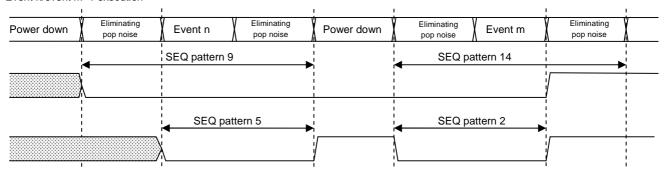

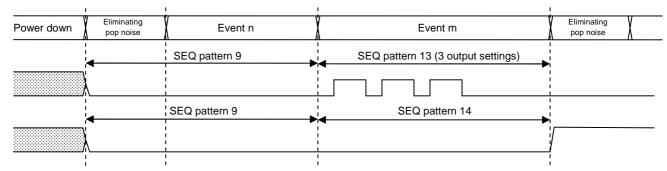

SEQ pattern 9: 09h

The "L" output is continued after event activation.

SEQ pattern 10: 0Ah

The "H" output is continued after event activation.

SEQ pattern 11: 0Bh

The "L" output is continued after event activation/POP noise elimination.

SEQ pattern 12: 0Ch

The "H" output is continued after event activation/POP noise elimination.

SEQ pattern 13: 0Dh

The "L" output is continued after event activation/POP noise elimination/voice reproduction processing end.

SEQ pattern 14: 0Eh

The "H" output is continued after event activation/POP noise elimination/voice reproduction processing end.

SEQ pattern 15: 0Fh

The "L" output is continued after event activation/POP noise elimination/voice reproduction/POP noise elimination processing end.

SEQ pattern 16: 10h

The "H" output is continued after event activation/POP noise elimination/voice reproduction/POP noise elimination processing end.

SEQ patterns 1 to 16 shown above are best suitable for power-down signal control of the amplifier and continuous LED-on during voice reproduction.

For the event of the SEQ output only, do not set SEQ patterns 1 to 16 shown above.

Set the delay time,  $t_{SEQD}$ , in the event management area. In addition, the pulse width setting and pulse output cycles setting are disabled.

When specifying two or more of SEQ patterns 1 to 16, set the delay time, t<sub>SEOD</sub>, to the equal value.

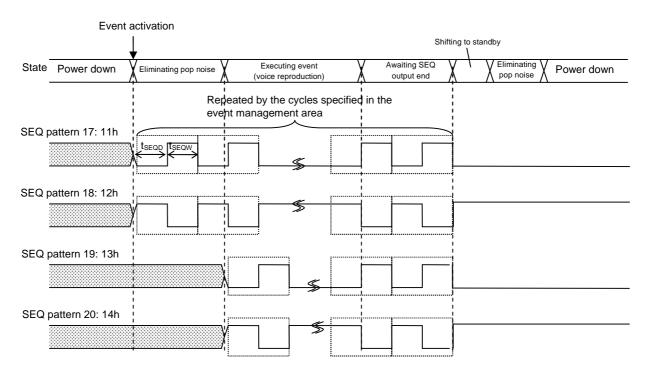

SEQ pattern 17: 11h, SEQ pattern 18: 12h

After event activation, the pulses having width tSEQW and period  $t_{SEQD} + t_{SEQW}$  are output by the set cycles.

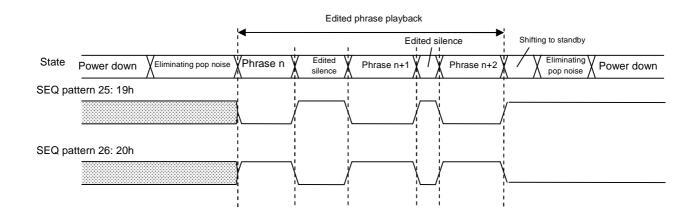

SEQ pattern 19: 13h, SEQ pattern 20: 14h

After event activation/POP noise elimination processing end, pulses having width  $t_{SEQW}$  and period  $t_{SEQD} + t_{SEQW}$  are output by the set cycles

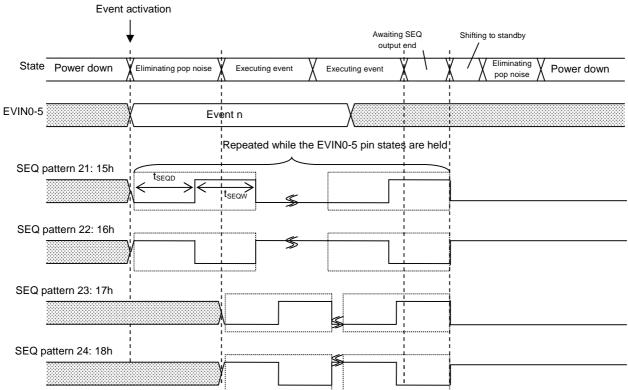

SEQ pattern 21: 15h, SEQ pattern 22: 16h

After event activation, pulses having width  $t_{SEQW}$  and period  $t_{SEQD} + t_{SEQW}$  are output repeatedly while the EVIN0 to 5 pin states are held.

SEQ pattern 23: 17h, SEQ pattern 24: 18h

After event activation/POP noise elimination processing end, pulses having width  $t_{SEQW}$  and period  $t_{SEQD} + t_{SEQW}$  are output repeatedly while the EVIN0 to 5 pin states are held.

Set the delay time  $(t_{SEQD})$ /pulse width  $(t_{SEQW})$ /pulse output cycles in the event management area. When SEQ patterns 21 to 23 are selected, the pulse output cycles setting is disabled.

SEQ patterns 17 to 24 shown above are best suitable for controlling the activation of peripheral circuits and LED-on/off.

For the event of the SEQ output only, do not set SEQ patterns 12, 20, 23, and 24 shown above.

Note: When SEQ patterns 17 to 24 and speech synthesis system 4bitOkiADPCM2 are selected, sampling frequencies up to 10.6 kHz must be selected. The sampling frequency of 12.8 kHz or 16 kHz should not be selected.

SEQ pattern 25: 19h

The "H" level is output when edited silence is played back and the "L" level is output when edited phrases are played back.

SEQ pattern 26: 1Ah

The "L" level is output when edited silence is played back and the "H" level is output when edited phrases are played back.

SEQ patterns 25 and 26 shown above are best suitable for detecting voice output levels and turning on LEDs. Only when the event of edited phrase playback is executed, the SEQ patterns 25 and 26 can be set.

In the case of the event of the only SEQ output or single phrase playback, do not set SEQ patterns 25 and 26. Delay time  $t_{SEOD}$ , pulse width  $t_{SEOW}$ , and pulse output cycles settings are disabled.

# **Example of SEQ Output**

### Event n/event m 1 execution

### Event n/event m consecutive executions

# **Setting of ROM Option**

The following table shows the items which can be set by using the ROM option (ROM data):

| Parameter                                                      | Setting value                                                                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Noise elimination time: t <sub>CHT</sub>                       | 8 ms/16 ms/32 ms/64 ms selectable                                                                                                                                         |

| Shift to AOUT output time: t <sub>DAR</sub> , t <sub>DAF</sub> | 32 ms/64 ms/128 ms/256 ms selectable                                                                                                                                      |

| Shift to standby time: t <sub>STB</sub>                        | 0 ms/128 ms/256 ms/512 ms selectable                                                                                                                                      |

| Setting of EVIN0-5 pin activation                              | Rise activation or fall activation can be selected.                                                                                                                       |

| EVIN0-5 pin input setting                                      | High-impedance input (CMOS input), pull-up input, or pull-down input selectable                                                                                           |

| Setting of the initial value of SEQ0-7 pin output              | Hi-Z, "L" output, or "H" output state selectable                                                                                                                          |

| Setting of SEQ0-7 pin output                                   | High-impedance output, CMOS output, Nch open drain, Pch open drain, or LED drive pin selectable                                                                           |

| Setting of use or unuse of SEQ0-7 pins                         | Use or unuse of the SEQ output of SEQ0-7 pins selectable                                                                                                                  |

| Setting of SEQEN pin output signal                             | Active-low or active-high selectable                                                                                                                                      |

| Setting of SEQRST pin input signal                             | Rise enable or fall enable can be selected.                                                                                                                               |

| Event execution mode                                           | Event 1-execution mode, event execution reservation mode, forcible event change mode, or repeat mode can be selected for each execution event.                            |

| Event execution contents                                       | Speech output execution, SEQ output execution, or speech output and SEQ output execution can be selected.                                                                 |

| Setting of the SEQ output pattern of SEQ0-7 pins               | SEQ pattern: 01h to 20h selectable                                                                                                                                        |

| Setting of the pulse output count of SEQ output pattern        | Once to 8-time output selectable                                                                                                                                          |

| Pulse output delay time of SEQ output pattern: tseqp           | 0 to 960 ms (setting value×(4×setting value)+4) selectable                                                                                                                |

| Pulse width of SEQ output pattern: t <sub>SEQW</sub>           | 0 to 960 ms (setting value×(4×setting value)+4) selectable                                                                                                                |

| Setting of PAUSE time after SEQRST                             | Setting of 0 to 5 sec (1-sec step), 10 to 50 sec (10-sec step), 1 to 5 min (1-min step), 10 to 50 min (10-min step), 1/2/3/6/12 hours, 1/2/3 days, or 1 week is possible. |

# **Configuration of Built-in ROM**

When the ML22300 series control mode is selected, the built-in ROM consists of the initialization, event management, and speech data areas.

When the MSM9800 series control mode is selected, the built-in ROM consists of the edit ROM, speech data management, and speech data areas.

Initialization area

Event management area

Speech data area

Edit ROM area

Speech data management area

Speech data area

Built-in ROM configuration when ML22300 series control mode is selected

Built-in ROM configuration when ML9800 series control mode is selected

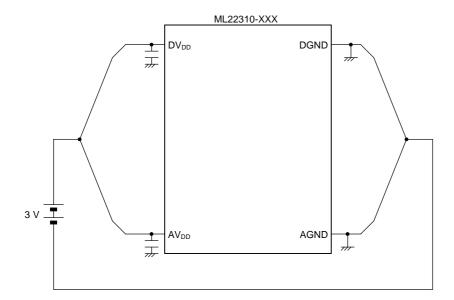

# **Power Supply Wiring**

The power supply of this LSI is divided into the following sections:

- Digital power supply (DVDD)

- Analog power supply (AVDD)

As shown below, supply the same power supply to DVDD and AVDD and separate the analog and digital power supplies by wiring.

# Power supply voltage = 3 V

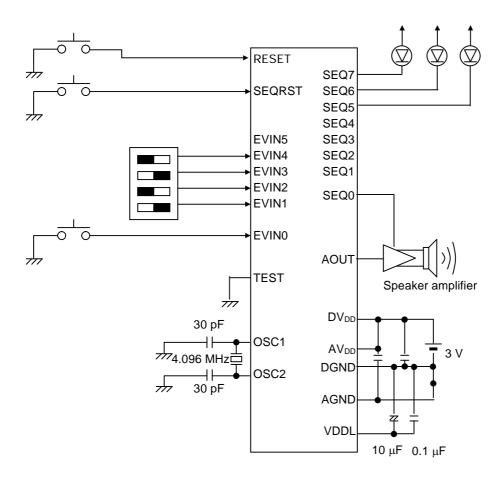

# **EXAMPLE OF APPLICATION CIRCUIT**

### PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact OKI's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

| Document          |              | Page                |                    |                       |  |

|-------------------|--------------|---------------------|--------------------|-----------------------|--|

| No.               | Date         | Previous<br>Edition | Current<br>Edition | Description           |  |

| PEDL22300FFULL-01 | Sep. 7, 2007 | _                   | -                  | Preliminary edition 1 |  |

### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. OKI assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by OKI, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

- Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2007 Oki Electric Industry Co., Ltd.