## **OKI Semiconductor**

FEDL9802-03-05-06

Issue Date: Nov. 22, 2004

# MSM9802/03/05-xxx

Voice Synthesis IC with Built-in Mask ROM

#### GENERAL DESCRIPTION

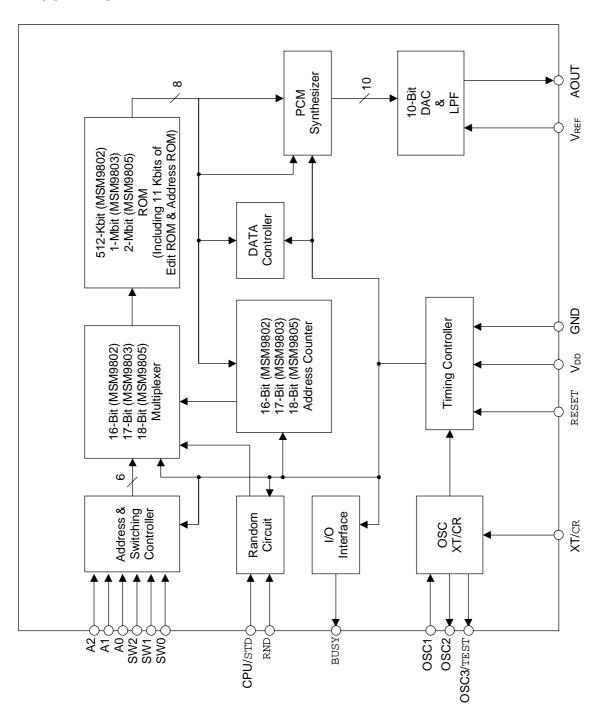

The MSM9802/03/05 is a PCM voice synthesis IC with built-in mask ROM.

This IC has two user selectable playback algorithms, OKI Non-linear PCM and straight PCM. It also contains a current mode 10-bit D/A converter and a low-pass filter.

External control has been made easy by the built-in edit ROM that can form sentences by linking phrases. By using Oki's Sound Analysis and Editing Tool, ROM data such as Phrase Control Table can be easily set, created, edited, and evaluated.

With the stand-alone mode/microcontroller interface mode switching pin, the MSM9802/03/05 can support various applications.

#### **FEATURES**

| Device ROM size* |          | Speech period (sec) |                    |                    |                     |  |  |

|------------------|----------|---------------------|--------------------|--------------------|---------------------|--|--|

| Device           | ROM SIZE | $f_{SAM} = 4.0kHz$  | $f_{SAM} = 6.4kHz$ | $f_{SAM} = 8.0kHz$ | $f_{SAM} = 16.0kHz$ |  |  |

| MSM9802          | 512Kbits | 16.0                | 10.0               | 8.0                | 4.0                 |  |  |

| MSM9803          | 1Mbit    | 32.4                | 20.2               | 16.2               | 8.1                 |  |  |

| MSM9805          | 2Mbits   | 65.1                | 40.7               | 32.5               | 16.2                |  |  |

- \* Actual voice ROM area is smaller by 11 Kbits.

- ROM custom

- 8-bit OKI nonlinear PCM method/8-bit straight PCM method

- Built-in edit ROM

- Random playback function

- Sampling frequency : 4.0 kHz/5.3 kHz/6.4 kHz/8.0 kHz/10.6 kHz/12.8 kHz/16.0 kHz

Note: If RC oscillation is selected, 10.6 kHz, 12.8 kHz, and 16.0 kHz

cannot be selected.

• Maximum number of phrases : 63 (Microcontroller interface mode)

56 (Stand-alone mode)

- Built-in current mode 10-bit D/A converter

- Built-in low-pass filter

- Standby function

- RC oscillation (256 kHz)/ceramic oscillation (4.096 MHz) selectable

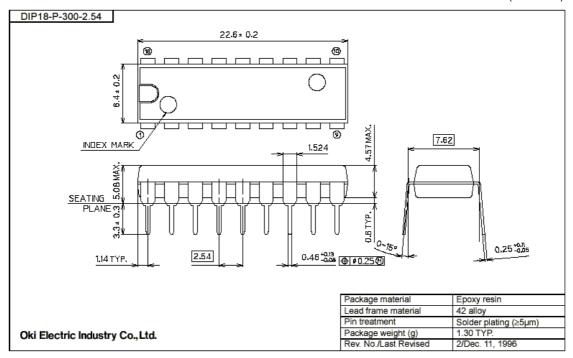

· Package options:

18-pin plastic DIP (DIP18-P-300-2.54) (MSM9802-xxxRS/MSM9803-xxxRS/

MSM9805-xxxRS)

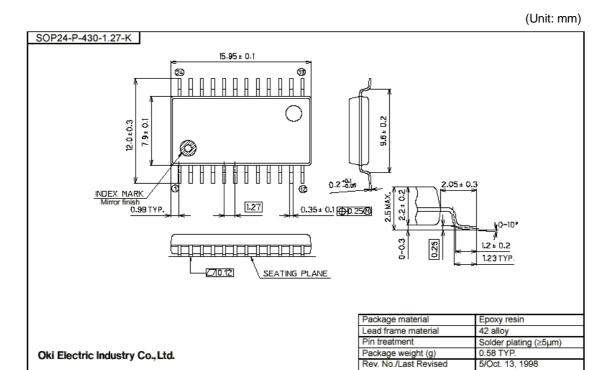

24-pin plastic SOP (SOP24-P-430-1.27-K) (MSM9802-xxxGS-K/MSM9803-xxxGS-K/

MSM9805-xxxGS-K)

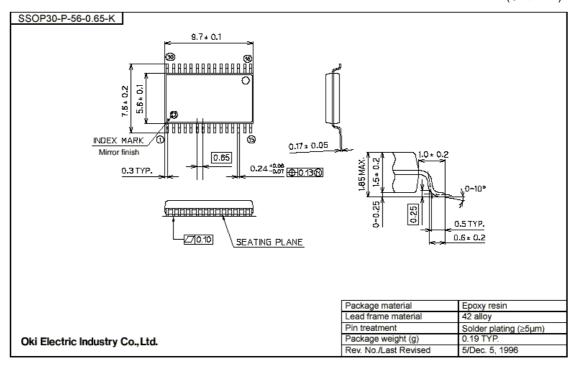

30-pin plastic SSOP (SSOP30-P-56-0.65-K) (MSM9802-xxxGS-AK/MSM9803-xxxGS-AK/

MSM9805-xxxGS-AK)

Chip

xxx indicates code number.

Note: This data sheet explains a stand-alone mode and a microcontroller interface mode, separately.

## **CONTENTS**

| (1) STAND-ALONE MODE                                   |    |

|--------------------------------------------------------|----|

| BLOCK DIAGRAM                                          | 3  |

| PIN CONFIGURATION                                      |    |

| PIN DESCRIPTIONS                                       | 6  |

| ABSOLUTE MAXIMUM RATINGS                               |    |

| RECOMMENDED OPERATING CONDITIONS                       | 8  |

| ELECTRICAL CHARACTERISTICS                             |    |

| TIMING DIAGRAMS                                        |    |

| FUNCTIONAL DESCRIPTION                                 |    |

| Playback Code Specification.                           |    |

| Pull-up/Pull-down Resistor                             |    |

| Stand-alone Mode                                       |    |

| APPLICATION CIRCUITS                                   |    |

|                                                        |    |

| (2) MICROCONTROLLER INTERFACE MODE                     |    |

| BLOCK DIAGRAM                                          | 21 |

| PIN CONFIGURATION                                      | 22 |

| PIN DESCRIPTIONS                                       | 24 |

| ABSOLUTE MAXIMUM RATINGS                               | 25 |

| RECOMMENDED OPERATING CONDITIONS                       | 25 |

| ELECTRICAL CHARACTERISTICS                             |    |

| TIMING DIAGRAMS                                        | 29 |

| FUNCTIONAL DESCRIPTION                                 | 31 |

| 1. Playback Code Specification                         |    |

| 2. Address Data                                        |    |

| 3. Stop Code                                           |    |

| 4. Generating Pseudo - BUSY Signal through NAR pin     | 33 |

| APPLICATION CIRCUIT                                    |    |

|                                                        |    |

| (3) COMMON                                             |    |

| Sampling Frequency                                     | 35 |

| Recording/Playback Time                                | 35 |

| Playback Method                                        | 36 |

| Phrase Control Table                                   | 37 |

| CR Oscillation                                         | 39 |

| Determining CR Contents                                | 40 |

| Ceramic Oscillation                                    | 40 |

| Low-pass Filter                                        | 42 |

| Standby Transition                                     | 43 |

| Voice Output Unit Equivalent Circuit (AOUT, VREF Pins) |    |

| D/A CONVERTER CURRENT CHARACTERISTICS                  | 45 |

| PAD CONFIGURATION                                      | 46 |

| PACKAGE DIMENSIONS                                     | 49 |

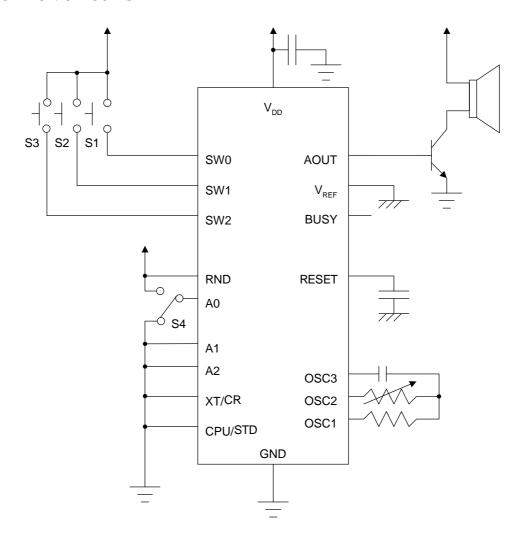

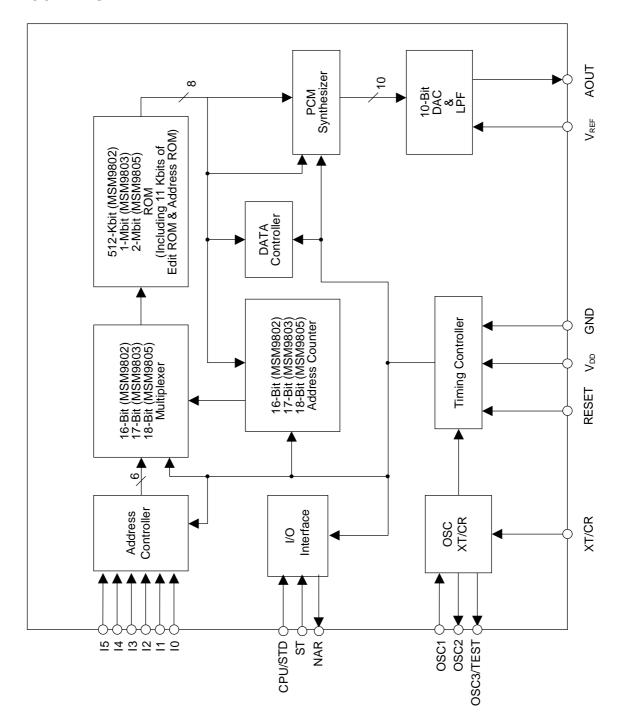

#### (1) STAND-ALONE MODE (CPU/STD: "L" LEVEL)

#### **BLOCK DIAGRAM**

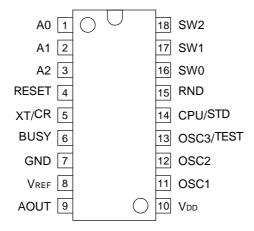

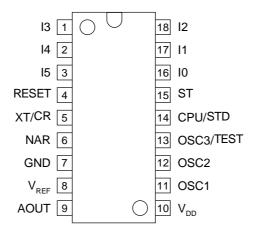

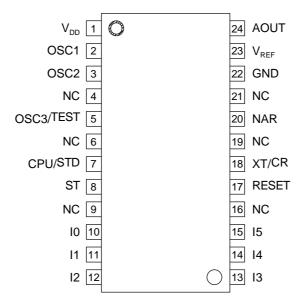

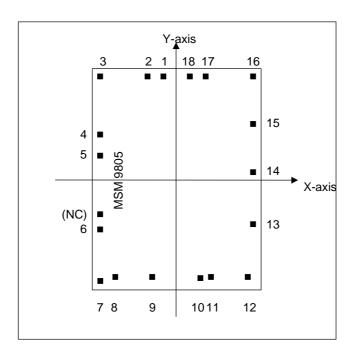

#### **PIN CONFIGURATION (TOP VIEW)**

18-Pin Plastic DIP

Note: Applicable to MSM9802-xxxRS, MSM9803-xxxRS, and MSM9805-xxxRS.

NC: No connection

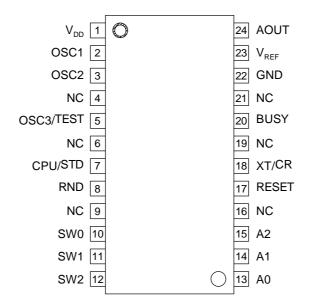

24-Pin Plastic SOP

Note: Applicable to MSM9802-xxxGS-K, MSM9803-xxxGS-K, and MSM9805-xxxGS-K.

FEDL9802-03-05-06

NC: No connection

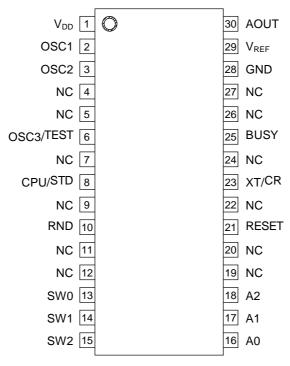

**30-Pin Plastic SSOP**

Note: Applicable to MSM9802-xxxGS-AK, MSM9803-xxxGS-AK, and MSM9805-xxxGS-AK.

## PIN DESCRIPTIONS

|     | Pin |      | Symbol    | Type | Description                                                                                                                                                                                                                                                     |  |

|-----|-----|------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DIP | SOP | SSOP | Symbol    | Type | Description                                                                                                                                                                                                                                                     |  |

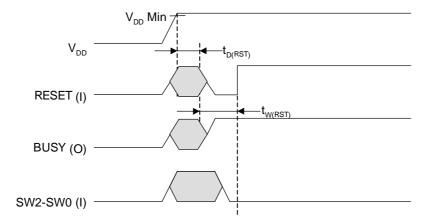

| 4   | 17  | 21   | RESET     | ı    | The IC enters the standby state if this pin is set to "L" level. At this time, oscillation stops and AOUT drives a current of 0mA and becomes GND level, then the IC returns to the initial state. Apply a "L" pulse upon power-on.                             |  |

|     |     |      |           |      | This pin has an internal pull-up resistor.                                                                                                                                                                                                                      |  |

|     |     |      |           |      | Outputs "L" level while voice is being played back.                                                                                                                                                                                                             |  |

| 6   | 20  | 25   | BUSY      | 0    | At power-on, this pin is at "H" level.                                                                                                                                                                                                                          |  |

| 5   | 18  | 23   | XT/cr     | ı    | XT/RC switching pin. Set to "H" level if ceramic oscillation is used.  Set to "L" level if RC oscillation is used.                                                                                                                                              |  |

| 14  | 7   | 8    | CPU/STD   |      | Microcontroller interface/stand-alone mode switching pin.                                                                                                                                                                                                       |  |

| 14  | ,   | 0    | CPO/SID   | ı    | Set to "L" level if the MSM9802/03/05 is used in stand-alone mode.                                                                                                                                                                                              |  |

| 8   | 23  | 29   | $V_{REF}$ | 1    | Volume setting pin. If this pin is set to GND level, the maximum current is forced in. If this pin is set to $V_{DD}$ level, the minimum current is forced in. A pull-down resistor of approx. $10\Omega$ is internally connected to this pin during operation. |  |

| 9   | 24  | 30   | AOUT      | 0    | Voice output pin.  The voice signals are output as current changes. In standl state, this pin drives a current of 0 mA and becomes GND leve                                                                                                                     |  |

| 7   | 22  | 28   | GND       | _    | Ground pin.                                                                                                                                                                                                                                                     |  |

| 10  | 1   | 1    | $V_{DD}$  | _    | Power supply pin. Insert a bypass capacitor of 0.1 $\mu F$ or more between $V_{DD}$ and GND pins.                                                                                                                                                               |  |

| 11  | 2   | 2    | OSC1      | ı    | Ceramic oscillator connection pin when ceramic oscillation is selected. RC connection pin when RC oscillation is selected. Input from this pin if external clock is used.                                                                                       |  |

| 12  | 3   | 3    | OSC2      | 0    | Ceramic oscillator connection pin when ceramic oscillation is selected.  RC connection pin when RC oscillation is selected.  Leave this pin open if external clock is used.  Outputs "L" level in standby state.                                                |  |

| 13  | 5   | 6    | OSC3/TEST | 0    | Leave this pin open when ceramic oscillation is used. RC connection pin when RC oscillation is selected. Outputs "H" level in standby state when RC oscillation is selected.                                                                                    |  |

| 15  | 8   | 10   | RND       | 1    | Random playback starts if RND pin is set to "L" level. Fetches addresses from random address generation circuit in the IC at fall of RND. Set to "H" level when the random playback function is not used. This pin has internal pull-up resistor.               |  |

| Pin   |       |       |         |      |                                                                                                                                                                                                  |

|-------|-------|-------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP   | SOP   | SSOP  | Symbol  | Type | Description                                                                                                                                                                                      |

| 16-18 | 10-12 | 13-15 | SW0-SW2 | I    | Phrase input pins corresponding to playback sound. If input changes, SW0 to SW2 pins fetch addresses after 16 ms and start voice synthesis.  Each of these pins has internal pull-down resistor. |

| 1-3   | 13-15 | 16-18 | A0-A2   | I    | Phrase input pins corresponding to playback sound.  Input logic of A0 pin becomes invalid if the random playback function is used.                                                               |

## ABSOLUTE MAXIMUM RATINGS

(GND = 0 V)

| Parameter            | Symbol           | Condition | Condition Rating          |    |

|----------------------|------------------|-----------|---------------------------|----|

| Power Supply Voltage | $V_{DD}$         | Ta = 25°C | -0.3 to +7.0              | V  |

| Input Voltage        | V <sub>IN</sub>  | 1a = 25 C | $-0.3$ to + $V_{DD}$ +0.3 | V  |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150               | °C |

#### RECOMMENDED OPERATING CONDITIONS

(GND = 0 V)

|                          |                   |                          |      |            |      | (0.15 - 0.1) |

|--------------------------|-------------------|--------------------------|------|------------|------|--------------|

| Parameter                | Parameter Symbol  |                          |      | Rating     | Unit |              |

| Power Supply Voltage     | $V_{DD}$          | _                        | 2    | 2.0 to 5.5 |      | V            |

| Operating Temperature    | T <sub>op</sub>   | _                        | _    | -40 to +85 |      | °C           |

| Moster Cleak Fraguency 1 | f <sub>OSC1</sub> | When crystal is selected | Min. | Тур.       | Max. | MHz          |

| Master Clock Frequency 1 |                   |                          | 3.5  | 4.096      | 4.5  | IVIIIZ       |

| Master Clock Frequency 2 | f <sub>OSC2</sub> | When RC is selected (*1) | 200  | 256        | 300  | kHz          |

<sup>\*1</sup> The accuracy of the oscillation frequency when RC oscillation is selected depends largely on the accuracy of the external R and C.

## **ELECTRICAL CHARACTERISTICS**

#### DC Characteristics (1)

$(V_{DD} = 5.0 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

|                                              |                   | (V <sub>DD</sub> = 5.0 V, GND = 0 V, Ta =                                  | ı    | 1    | ı    | <del>.                                      </del> |

|----------------------------------------------|-------------------|----------------------------------------------------------------------------|------|------|------|----------------------------------------------------|

| Parameter                                    | Symbol            | Condition                                                                  | Min. | Тур. | Max. | Unit                                               |

| "H" Input Voltage                            | V <sub>IH</sub>   | _                                                                          | 4.2  |      | _    | V                                                  |

| "L" Input Voltage                            | $V_{IL}$          | _                                                                          | _    | _    | 0.8  | V                                                  |

| "H" Output Voltage                           | V <sub>OH</sub>   | $I_{OH} = -1 \text{ mA}$                                                   | 4.6  | _    | _    | V                                                  |

| "L" Output Voltage                           | V <sub>OL</sub>   | $I_{OL} = 2 \text{ mA}$                                                    | _    | _    | 0.4  | V                                                  |

| "H" Input Current 1                          | I <sub>IH1</sub>  | $V_{IH} = V_{DD}$                                                          | _    | _    | 10   | μΑ                                                 |

| "H" Input Current 2 *1                       | I <sub>IH2</sub>  | Internal pull-down resistor                                                | 30   | 90   | 200  | μΑ                                                 |

| "H" Input Current 3                          | I <sub>IH3</sub>  | Applies to OSC1 pin only. $V_{IH} = V_{DD}$                                | _    | _    | 15   | μΑ                                                 |

| "L" Input Current 1                          | I <sub>IL1</sub>  | V <sub>IL</sub> = GND                                                      | -10  | _    | _    | μΑ                                                 |

| "L" Input Current 2 *2                       | I <sub>IL2</sub>  | Internal pull-up resistor                                                  | -200 | -90  | -30  | μΑ                                                 |

| Dynamic Supply Current 1 *3                  | I <sub>DD1</sub>  | $V_{REF} = V_{DD}$ , AOUT bias voltage = 0V                                | _    | 0.4  | 1    | mA                                                 |

| Dynamic Supply Current 2  *4                 | I <sub>DD2</sub>  | At maximum output current  V <sub>REF</sub> = GND, AOUT bias  voltage = 0V | _    | _    | 16   | mA                                                 |

| Standby Current                              | ı                 | $Ta = -40 \text{ to } +70^{\circ}\text{C}$                                 | _    | _    | 10   | μΑ                                                 |

| Standby Current                              | I <sub>DS</sub>   | Ta = 70 to 85°C                                                            | _    | _    | 50   | μΑ                                                 |

| AOUT Output Current                          | I <sub>AOUT</sub> | At maximum output current, $V_{REF} = GND,$ AOUT bias voltage = 0V         | 6    | 9.5  | 15   | mA                                                 |

| V <sub>REF</sub> Pin Pull-down<br>Resistance | $R_{VREF}$        | _                                                                          | 7    | 10   | 13   | kΩ                                                 |

<sup>\*1</sup> Applicable to SW0-SW2

\*2 Applicable to RESET, RND

\*3 Dynamic supply current (excluding DAC output current)

\*4 Dynamic supply current at maximum output current

## DC Characteristics (2)

$(V_{DD} = 3.1 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter                                    | Symbol            | Condition                                                            | Min. | Тур. | Max. | Unit |

|----------------------------------------------|-------------------|----------------------------------------------------------------------|------|------|------|------|

| "H" Input Voltage                            | V <sub>IH</sub>   | _                                                                    | 2.7  | _    | _    | V    |

| "L" Input Voltage                            | V <sub>IL</sub>   | _                                                                    | _    | _    | 0.5  | V    |

| "H" Output Voltage                           | V <sub>OH</sub>   | I <sub>OH</sub> = -1 mA                                              | 2.6  | _    | _    | V    |

| "L" Output Voltage                           | V <sub>OL</sub>   | $I_{OL} = 2 \text{ mA}$                                              | _    | _    | 0.4  | V    |

| "H" Input Current 1                          | I <sub>IH1</sub>  | $V_{IH} = V_{DD}$                                                    | 1    | 1    | 10   | μΑ   |

| "H" Input Current 2 *1                       | I <sub>IH2</sub>  | Internal pull-down resistor                                          | 10   | 30   | 100  | μΑ   |

| "H" Input Current 3                          | I <sub>IH3</sub>  | Applies to OSC1 pin only. $V_{IH} = V_{DD}$                          |      |      | 15   | μΑ   |

| "L" Input Current 1                          | I <sub>IL1</sub>  | $V_{IL} = GND$                                                       | -10  |      |      | μΑ   |

| "L" Input Current 2 *2                       | I <sub>IL2</sub>  | Internal pull-up resistor                                            | -100 | -30  | -10  | μΑ   |

| Dynamic Supply Current 1 *3                  | I <sub>DD1</sub>  | $V_{REF} = V_{DD}$ , AOUT bias voltage = 0V                          | _    | 0.15 | 0.5  | mA   |

| Dynamic Supply Current 2 *4                  | I <sub>DD2</sub>  | At maximum output current $V_{REF} = GND$ , AOUT bias voltage = 0V   | _    |      | 5.5  | mA   |

| Standby Current                              | 1                 | $Ta = -40 \text{ to } +70^{\circ}\text{C}$                           | _    | _    | 5    | μΑ   |

| Standby Current                              | I <sub>DS</sub>   | Ta = 70 to 85°C                                                      | 1    | 1    | 20   | μΑ   |

| AOUT Output Current                          | I <sub>AOUT</sub> | At maximum output current, $V_{REF} = GND,$ AOUT bias voltage = $0V$ | 1.4  | 3.2  | 5    | mA   |

| V <sub>REF</sub> Pin Pull-down<br>Resistance | R <sub>VREF</sub> | _                                                                    | 7    | 10   | 13   | kΩ   |

<sup>\*1</sup> Applicable to SW2-SW0

\*2 Applicable to RESET, RND

\*3 Dynamic supply current (excluding DAC output current)

\*4 Dynamic supply current at maximum output current

## **AC Characteristics**

$(V_{DD} = 5.0 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                       | Symbol                              | Condition                       | Min. | Тур. | Max. | Unit |

|---------------------------------|-------------------------------------|---------------------------------|------|------|------|------|

| Master Clock Duty Cycle         | f <sub>duty</sub>                   |                                 | 40   | 50   | 60   | %    |

| RESET Input Pulse Width         | t <sub>w(RST)</sub>                 | _                               | 10   | _    | _    | μs   |

| RESET Input Time After Power-on | $t_{D(RST)}$                        |                                 | 0    | _    | _    | μs   |

| RND Input Pulse Width           | t <sub>w(RAN)</sub>                 |                                 | 100  | _    | _    | μs   |

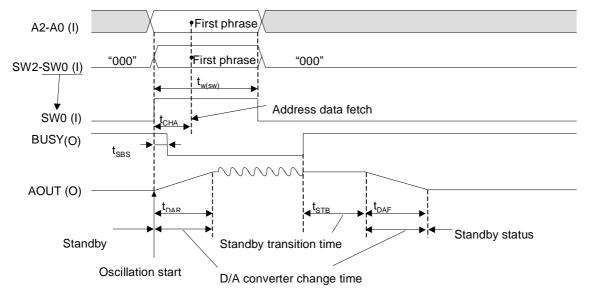

| SW0-SW2 Input Pulse Width       | t <sub>w(SW)</sub>                  | — (note)                        | 16   | _    | _    | ms   |

| BUSY Output Time                | t <sub>SBS</sub>                    | _                               | _    | _    | 10   | μs   |

| Chattering Prevention Time 1    | t <sub>CHA</sub>                    | — (note)                        | 14   | 15   | 16   | ms   |

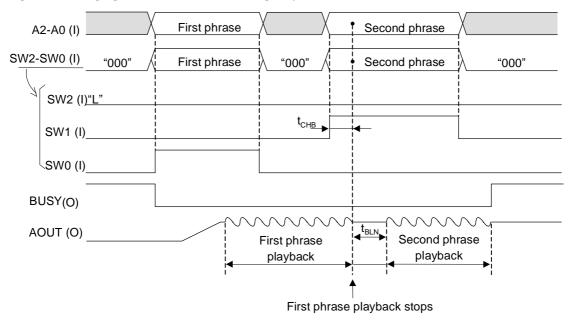

| Chattering Prevention Time 2    | t <sub>СНВ</sub>                    | — (note)                        | _    | _    | 16   | ms   |

| D/A Converter Change Time       | t <sub>DAR</sub> , t <sub>DAF</sub> | — (note)                        | 60   | 64   | 68   | ms   |

| Standby Transition Time         | t <sub>STB</sub>                    | — (note)                        | 200  | 250  | 300  | ms   |

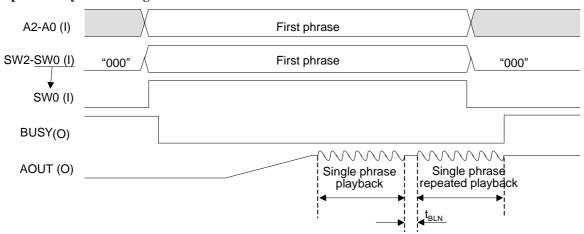

| Silence Time Between<br>Phrases | t <sub>BLN</sub>                    | f <sub>SAM</sub> = 8 kHz (note) | 350  | 375  | 500  | μs   |

| Random Address Fetch Time       | t <sub>RA</sub>                     | — (note)                        | 15   | 16   | 17   | μs   |

(Note) Proportional to master the periods of oscillation frequencies  $f_{\text{OSC1}}$  and  $f_{\text{OSC2}}$ . The rated values show values when the standard master oscillation frequency is used.

#### **TIMING DIAGRAMS**

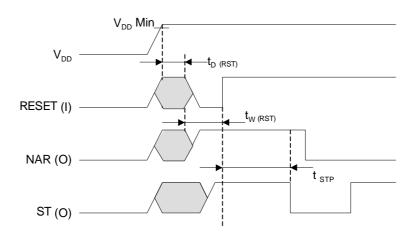

#### **AC Characteristics at Power-On**

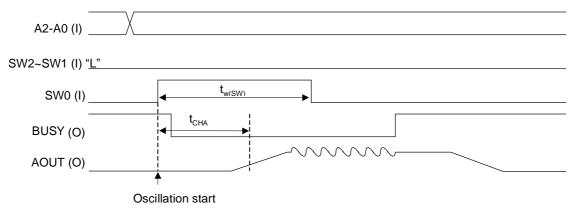

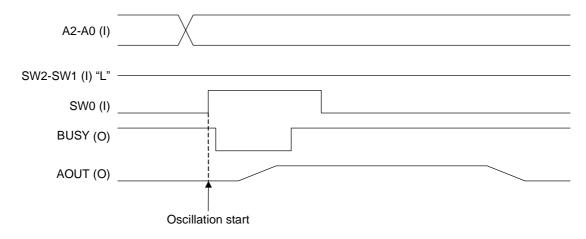

## AC Characteristics in Standby Status and when the IC is Activated

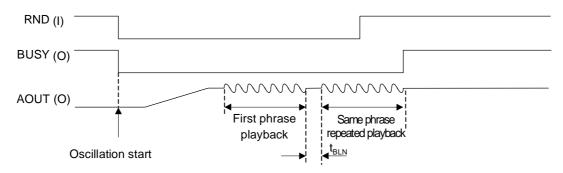

## **Repeated Playback Timing**

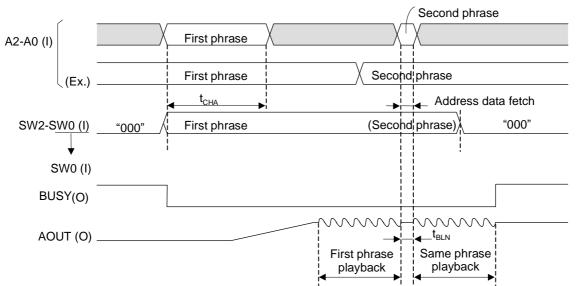

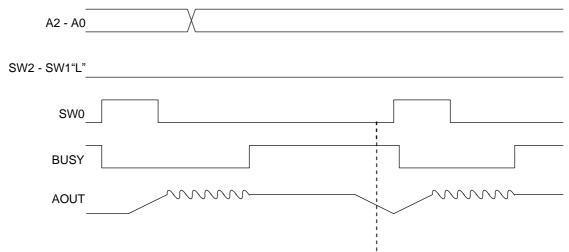

#### Timing when Changing from SW2 to SW0 During Playback

#### Repeated Playback Timing for Random Playback

## Timing when Changing from A2 to A0 During Playback

#### **FUNCTIONAL DESCRIPTION**

#### **Playback Code Specification**

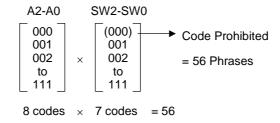

The user can specify a maximum of 56 phrases. Table 1.1 shows the settings by the A2-A0 and SW2-SW0 pins.

A2-A0

SW2-SW0

Code Details

000

000

Inhibit code

001

User-specified phrase

111

111

**Table 1.1 User-specified Phrases**

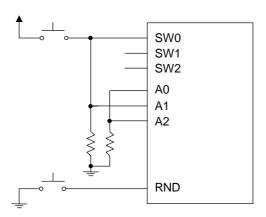

#### Pull-up/Pull-down Resistor

The RESET and RND pins have internal pull-up resistors and the SW2-SW0 pins have internal pull-down resistors.

#### **Stand-alone Mode**

In a stand-alone mode, the SW input interface function and the random playback function can be used.

#### SW input interface

With the SW input interface, speech synthesis starts when the state of the SW2-SW0 pins has changed. To prevent chattering, the address data is latched 16 ms ( $t_{CHA}$ ) after the state of SW2-SW0 has changed. Voice synthesis does not start if the state of the A2-A0 pins has changed. Set the RND pin to "H" level if the random playback function is not used.

Set the A2-A0 pins to "L" level at power-on or at reset.

The SW input interface is effective when the MSM9802/03/05 is operated using a push-button switch. Voice synthesis starts when an address is changed by pressing the push-button switch. If the push-button switch is released during playback, then playback stops after the current phrase is completed.

Figure 3.1 SW Input Interface Single-Phrase Playback Timing

If playback is attempted at an unused address in the phrases, AOUT goes to 1/2 I<sub>AOUT</sub> and playback does not occur. Figure 3.2 shows the timing.

Figure 3.2 Timing when Playback is Attempted at an Unused Phrase Address

In the SW input interface, no phrase is triggered when SW2 to SW0 are all set to "0". Therefore, when the circuit consists of a diode matrices that use push-button switches, the maximum playback phrases are 56 phrases.

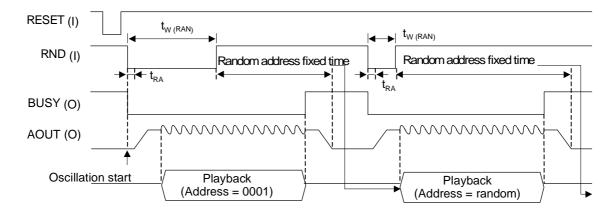

#### Random playback function

The random playback function randomly generates 15 different addresses corresponding to the four bits of the addresses of A0 and SW2-SW0 (except ALL "L") on the IC, after which playback commences.

Therefore, any input to A0 and SW2 to SW0 pins from external control is invalid. Hold these 4 pins either "H" or "L" level. SW2 to SW0 pins may be held open as they have internal pull-down resistor.

Playback may not occur if all the 15 addresses have not been assigned a phrase. Care must be taken when creating ROM data.

For example, when four phrases, "sunny", "rainy", "cloudy", and "snowy", are to be played randomly, set the phrases as shown in Table 3.1 in which a phrase is assigned to all the 15 addresses. The four phrases are then played back at random as shown below.

| A2, A1 | A0, SW2-SW0 | Phrase |  |

|--------|-------------|--------|--|

|        | 0001        | sunny  |  |

|        | 0010        | rainy  |  |

|        | 0011        | cloudy |  |

| 00     | 0100        | snowy  |  |

| 00     | 0101        | sunny  |  |

|        |             |        |  |

|        | 1110        | rainy  |  |

|        | 1111        | snowy  |  |

**Table 3.1 Random Address Setup Example**

Random playback starts when the timing shown in Figure 3.3 is input to the RND pin. A random address is fixed based on the "H" level time of the RND pin during IC oscillation. Random address is captured at the fall of the RND pin, and voice playback commences. Therefore, when power is turned on, or when RESET is input, the phrase at fixed address "0001" is played while the random counter remains initialized until random playback is initiated.

Figure 3.3 Random Address Capture

| A2, A1 | A0, SW2 to SW0 | Phrase (Sample) |  |  |

|--------|----------------|-----------------|--|--|

|        | 0001           | Hit             |  |  |

|        | 0010           | Hit             |  |  |

| 00     | 0011           | Hit             |  |  |

| 00     | 0100           | Out             |  |  |

|        |                |                 |  |  |

|        | 1111           | Out             |  |  |

|        | 0001           | Hit             |  |  |

|        | 0010           | Out             |  |  |

| 04     | 0011           | Out             |  |  |

| 01     | 0100           | Out             |  |  |

|        |                |                 |  |  |

|        | 1111           | Out             |  |  |

|        | 0001           | White           |  |  |

|        | 0010           | Black           |  |  |

| 40     | 0011           | Red             |  |  |

| 10     | 0100           | Blue            |  |  |

|        |                |                 |  |  |

|        | 1111           | Green           |  |  |

|        | 0001           |                 |  |  |

| 11     |                |                 |  |  |

|        | 1111           |                 |  |  |

**Table 3.2 Random Playback Address**

For a random address, 15 phrases can be set for each logical condition of addresses A2 and A1 (i.e., "00", "01", "10", and "11").

In random playback, the four logic states ("000000", "010000", "100000" and "110000") in user-specified phrases cannot be used. Take it into consideration when creating ROM data.

A random address is set by the "H" level time of the RND pin, so if the same pulse width is input by microcontroller, the random address fixed time becomes constant, and a random phrase may not be played under these conditions. The random address fixed time must be inconsistent in order to produce random playback.

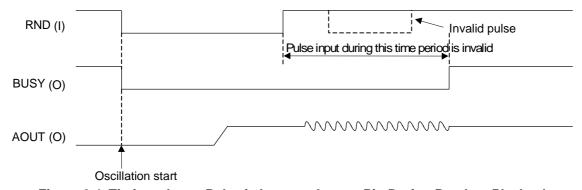

Figure 3.4 Timing when a Pulse is Input to the RND Pin During Random Playback

**Table 3.3 Random Playback and Stop Address**

| A2, A1 | A0, SW2-SW0 *     | Code Details                              |

|--------|-------------------|-------------------------------------------|

| 00     | 0001<br> <br>1111 | Random playback address<br>(15 addresses) |

| 01     | 0001              | Stop address                              |

<sup>\*</sup> Address(es) corresponding to the A0 and SW2-SW0 pins

Figure 3.5 Circuit Example for Random Playback Stop

An unused user-specified address is used as a stop address, therefore the IC can enter standby without voice playback, as shown in Figure 3.2.

## **APPLICATION CIRCUITS**

|          |    | A2 | A1 | A0 | SW2 | SW1 | SW0 | Address [HEX] |

|----------|----|----|----|----|-----|-----|-----|---------------|

|          | S1 | 0  | 0  | 0  | 0   | 0   | 1   | 01            |

| S4 = "L" | S2 | 0  | 0  | 0  | 0   | 1   | 0   | 02            |

|          | S3 | 0  | 0  | 0  | 1   | 0   | 0   | 04            |

|          | S1 | 0  | 0  | 1  | 0   | 0   | 1   | 09            |

| S4 = "H" | S2 | 0  | 0  | 1  | 0   | 1   | 0   | 0A            |

|          | S3 | 0  | 0  | 1  | 1   | 0   | 0   | 0C            |

**Application Circuit for Playing Six Phrases Using Four Switches**

**Application Circuit Using Switches**

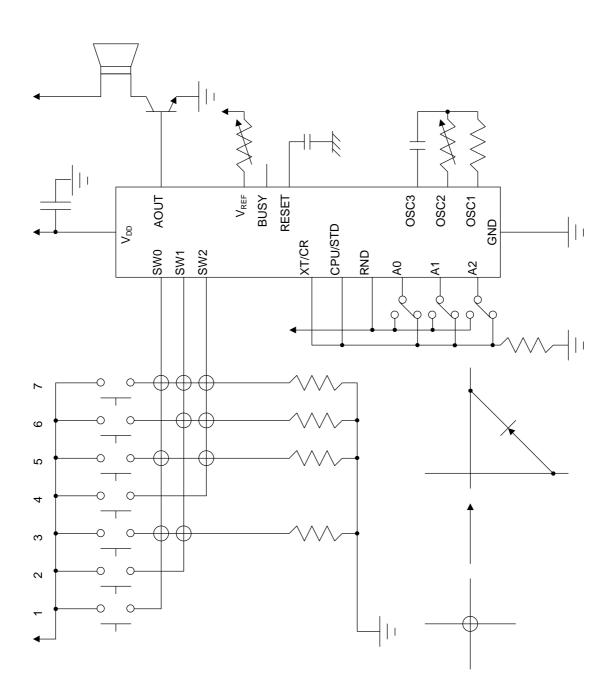

## (2) MICROCONTROLLER INTERFACE MODE (CPU/std: "H" LEVEL)

#### **BLOCK DIAGRAM**

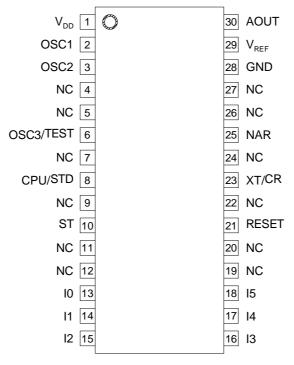

#### **PIN CONFIGURATION (TOP VIEW)**

18-Pin Plastic DIP

Note: Applicable to MSM9802-xxxRS, MSM9803-xxxRS, and MSM9805-xxxRS.

NC: No connection

24-Pin Plastic SOP

Note: Applicable to MSM9802-xxxGS-K, MSM9803-xxxGS-K, and MSM9805-xxxGS-K.

FEDL9802-03-05-06

NC: No connection

30-Pin Plastic SSOP

Note: Applicable to MSM9802-xxxGS-AK, MSM9803-xxxGS-AK, and MSM9805-xxxGS-AK.

## PIN DESCRIPTIONS

|              | Pin   |       | Symbol Type |      | Description                                                                                                                                                                                                                                                                      |

|--------------|-------|-------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP          | SOP   | SSOP  | Symbol      | Type | Description                                                                                                                                                                                                                                                                      |

| 4            | 17    | 21    | RESET       | I    | The IC enters the standby state if this pin is set to "L" level. At this time, oscillation stops and AOUT drives a current of 0 mA and becomes GND level, then the IC returns to the initial state. Apply a "L" pulse upon power-on.  This pin has an internal pull-up resistor. |

| 6            | 20    | 25    | NAR         | 0    | Signal output pin that indicates whether the 6-bit LATCH (see Block Diagram) is idle. NAR at "H" level indicates that the LATCH is empty and ST input is enabled.                                                                                                                |

| 5            | 18    | 23    | XT/CR       | I    | XT/CR switching pin. Set to "H" level if ceramic oscillation is used. Set to "L" level if CR oscillation is used.                                                                                                                                                                |

| 14           | 7     | 8     | CPU/STD     | ı    | Microcontroller interface/stand-alone mode switching pin. Set to "H" level if the MSM9802/03/05 is used in microcontroller interface mode.                                                                                                                                       |

| 8            | 23    | 29    | $V_{REF}$   | ı    | Volume setting pin. If this pin is set to GND level, the maximum current is forced in, and if set to $V_{DD}$ level, the minimum current is forced in. An approx. 10 k $\Omega$ pull-down resistor is internally connected to this pin during operation.                         |

| 9            | 24    | 30    | AOUT        | 0    | Voice output pin.  The voice signals are output as current changes. In standby state, this pin drives a current of 0 mA and becomes GND level.                                                                                                                                   |

| 7            | 22    | 28    | GND         | _    | Ground pin.                                                                                                                                                                                                                                                                      |

| 10           | 1     | 1     | $V_{DD}$    | _    | Power supply pin. Insert a bypass capacitor of 0.1 $\mu F$ or more between this pin and the GND pin.                                                                                                                                                                             |

| 11           | 2     | 2     | OSC1        | ı    | Ceramic oscillator connection pin when ceramic oscillation is selected. CR connection pin when CR oscillation is selected. Input from this pin if external clock is used.                                                                                                        |

| 12           | 3     | 3     | OSC2        | 0    | Ceramic oscillator connection pin when ceramic oscillation is selected.  CR connection pin when CR oscillation is selected.  Leave this pin open if external clock is used.  Outputs "L" level in standby state.                                                                 |

| 13           | 5     | 6     | OSC3/TEST   | 0    | Leave this pin open when ceramic oscillation is used. CR connection pin when CR oscillation is selected. Outputs "H" level in standby state when CR oscillation is selected.                                                                                                     |

| 15           | 8     | 10    | ST          | ı    | Voice synthesis starts at fall of ST, and addresses I0 to I5 are fetched at rise of ST. Input ST when NAR, the status signal, is at "H" level.  This pin has internal pull-up resistor.                                                                                          |

| 16-18<br>1-3 | 10-15 | 13-18 | 10 - 15     | I    | Phrase input pins corresponding to playback sound.                                                                                                                                                                                                                               |

## ABSOLUTE MAXIMUM RATINGS

(GND = 0V)

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage | $V_{DD}$         | Ta = 25°C | -0.3 to +7.0                 | V    |

| Input Voltage        | V <sub>IN</sub>  | 1a = 25 C | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                  | °C   |

## RECOMMENDED OPERATING CONDITIONS

(GND = 0V)

| Parameter                        | Symbol Condition  |                          | Rating |            |      | Unit |

|----------------------------------|-------------------|--------------------------|--------|------------|------|------|

| Power Supply Voltage             | $V_{DD}$          | _                        |        | 2.0 to 5.5 | 5    | V    |

| Operating Temperature            | T <sub>op</sub>   | _                        | _      | -40 to +8  | 5    | °C   |

| Original Oscillation Fraguency 1 | f                 | When envetal is colocted | Min.   | Тур.       | Max. | MHz  |

| Original Oscillation Frequency 1 | t <sub>OSC1</sub> | When crystal is selected | 3.5    | 4.096      | 4.5  |      |

| Original Oscillation Frequency 2 | f <sub>OSC2</sub> | When CR is selected (*1) | 200    | 256        | 300  | kHz  |

<sup>\*1</sup> The accuracy of the oscillation frequency when CR oscillation is selected depends largely on the accuracy of the external R and C.

## **ELECTRICAL CHARACTERISTICS**

#### DC Characteristics (1)

$(V_{DD} = 5.0 \text{ V}, \text{GND} = 0 \text{ V}, \text{Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

|                                              |                                  | (100 110 1, 111 11 11 11                                             |      | -,   |      | o opoomou |

|----------------------------------------------|----------------------------------|----------------------------------------------------------------------|------|------|------|-----------|

| Parameter Symbol                             |                                  | Condition                                                            | Min. | Тур. | Max. | Unit      |

| "H" Input Voltage                            | H" Input Voltage V <sub>IH</sub> |                                                                      | 4.2  | _    | _    | V         |

| "L" Input Voltage                            | $V_{IL}$                         | _                                                                    | _    | _    | 0.8  | V         |

| "H" Output Voltage                           | V <sub>OH</sub>                  | $I_{OH} = -1 \text{ mA}$                                             | 4.6  | _    | _    | V         |

| "L" Output Voltage                           | V <sub>OL</sub>                  | $I_{OL} = 2 \text{ mA}$                                              | _    | _    | 0.4  | V         |

| "H" Input Current 1                          | I <sub>IH1</sub>                 | $V_{IH} = V_{DD}$                                                    |      | _    | 10   | μΑ        |

| "H" Input Current 2                          |                                  | Applies to OSC1 pin only. $V_{IH} = V_{DD}$                          | _    | _    | 15   | μΑ        |

| "L" Input Current 1                          | I <sub>IL1</sub>                 | V <sub>IL</sub> = GND                                                | -10  | _    | _    | μA        |

| "L" Input Current 2 *1                       | I <sub>IL2</sub>                 | Internal pull-up resistor                                            | -200 | -90  | -30  | μA        |

| Dynamic Supply Current 1 *2                  | I <sub>DD1</sub>                 | $V_{REF} = V_{DD}$ , AOUT bias voltage = 0V                          | _    | 0.4  | 1    | mA        |

| Dynamic Supply Current 2 *3                  | l lnna                           |                                                                      | _    | _    | 16   | mA        |

| Standby Current                              | I <sub>DS</sub>                  | Ta = -40 to +70°C                                                    | _    | _    | 10   | μΑ        |

|                                              |                                  | Ta = 70 to 85°C                                                      | _    | _    | 50   | μΑ        |

| AOUT Output Current I <sub>AOUT</sub>        |                                  | At maximum output current, $V_{REF} = GND,$ $AOUT bias voltage = 0V$ |      | 9.5  | 15   | mA        |

| V <sub>REF</sub> Pin Pull-down<br>Resistance | $R_{VREF}$                       | _                                                                    | 7    | 10   | 13   | kΩ        |

<sup>\*1</sup> Applicable to RESET, ST

<sup>\*2</sup> Dynamic supply current (excluding DAC output current)

\*3 Dynamic supply current at maximum output current

## DC Characteristics (2)

$(V_{DD} = 3.1 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter                                 | Symbol            | Condition                                                            | Min. | Тур. | Max. | Unit     |

|-------------------------------------------|-------------------|----------------------------------------------------------------------|------|------|------|----------|

| "H" Input Voltage                         | V <sub>IH</sub>   | _                                                                    | 2.7  | _    | _    | V        |

| "L" Input Voltage                         | V <sub>IL</sub>   | _                                                                    | _    | 1    | 0.5  | V        |

| "H" Output Voltage                        | V <sub>OH</sub>   | $I_{OH} = -1 \text{ mA}$                                             | 2.6  |      | _    | >        |

| "L" Output Voltage                        | $V_{OL}$          | $I_{OL} = 2 \text{ mA}$                                              | _    |      | 0.4  | <b>V</b> |

| "H" Input Current 1                       | I <sub>IH1</sub>  | $V_{IH} = V_{DD}$                                                    | _    | _    | 10   | μΑ       |

| "H" Input Current 2                       | I <sub>IH2</sub>  | Applies to OSC1 pin only. $V_{IH} = V_{DD}$                          | _    | _    | 15   | μΑ       |

| "L" Input Current 1                       | I <sub>IL1</sub>  | V <sub>IL</sub> = GND                                                | -10  | _    | _    | μΑ       |

| "L" Input Current 2 *1                    | I <sub>IL2</sub>  | Internal pull-up resistor                                            | -100 | -30  | -10  | μΑ       |

| Dynamic Supply Current 1 *2               | I <sub>DD1</sub>  | $V_{REF} = V_{DD}$ , AOUT bias voltage = 0V                          | _    | 0.15 | 0.5  | mA       |

| Dynamic Supply Current 2 *3               | I <sub>DD2</sub>  | At maximum output current $V_{REF} = GND$ , AOUT bias voltage = 0V   | _    | _    | 5.5  | mA       |

| Standby Current                           | ı                 | $Ta = -40 \text{ to } +70^{\circ}\text{C}$                           | _    | _    | 5    | μΑ       |

| Standby Current                           | I <sub>DS</sub>   | Ta = 70 to 85°C                                                      | _    | 1    | 20   | μΑ       |

| AOUT Output Current                       | I <sub>AOUT</sub> | At maximum output current, $V_{REF} = GND,$ AOUT bias voltage = $0V$ | 1.4  | 3.2  | 5    | mA       |

| V <sub>REF</sub> Pin Pull-down Resistance | R <sub>VREF</sub> | _                                                                    | 7    | 10   | 13   | kΩ       |

<sup>\*1</sup> Applicable to RESET, ST

<sup>\*2</sup> Dynamic supply current (excluding DAC output current)

\*3 Dynamic supply current at maximum output currents

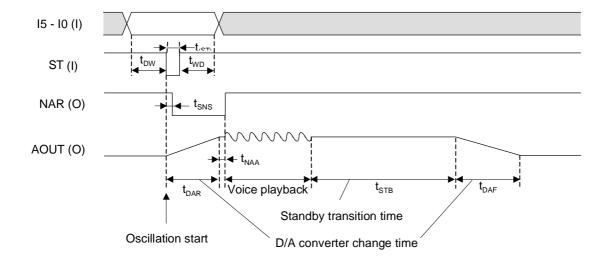

## **AC Characteristics**

$(V_{DD} = 5.0 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                                        | Symbol             | Condition                                | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|--------------------|------------------------------------------|------|------|------|------|

| Master Clock Duty Cycle                          | f <sub>duty</sub>  | _                                        | 40   | 50   | 60   | %    |

| RESET Input Pulse Width                          | $t_{w(RST)}$       | _                                        | 10   | _    | _    | μs   |

| RESET Input Time After Power-on                  | $t_{D(RST)}$       |                                          | 0    | _    | _    | μs   |

| ST Signal Setup Time                             | t <sub>STP</sub>   | At power-on                              | 1    | _    | _    | μs   |

| ST Input Pulse Width                             | $t_{(ST)}$         |                                          | 0.35 | _    | 2000 | μs   |

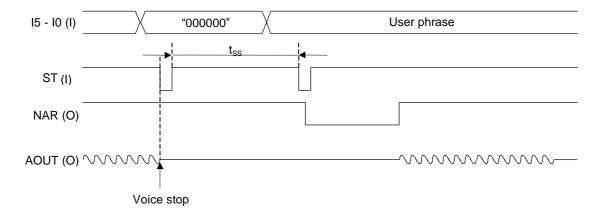

| ST-ST Pulse Interval                             | t <sub>SS</sub>    | Upon entering the stop code (note)       | 40   |      |      | μs   |

| Data Setup Time                                  | $t_{DW}$           |                                          | 1    | _    | _    | μs   |

| Data Hold Time                                   | $t_{WD}$           |                                          | 1    | _    | _    | μs   |

| NAR Output Time (1)                              | t <sub>SNS</sub>   | $f_{SAM} = 8 \text{ kHz}$                |      | _    | 10   | μs   |

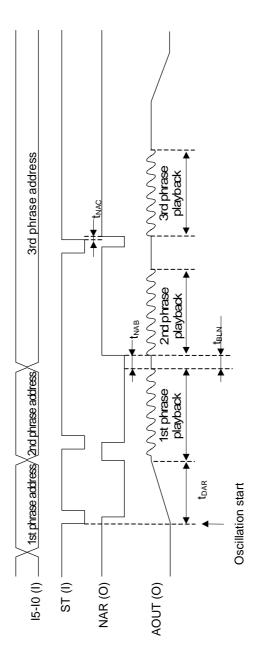

| NAR Output Time (2)                              | t <sub>NAA</sub>   | $f_{SAM} = 8 \text{ kHz} \text{ (note)}$ | 350  | 375  | 400  | μs   |

| NAR Output Time (3)                              | t <sub>NAB</sub>   | $f_{SAM} = 8 \text{ kHz} \text{ (note)}$ | 315  | 440  | 500  | μs   |

| NAR Output Time (4)                              | t <sub>NAC</sub>   | $f_{SAM} = 8 \text{ kHz} \text{ (note)}$ | 350  | 375  | 500  | μs   |

| D/A Converter Change<br>Time                     | $t_{DAR}, t_{DAF}$ | — (note)                                 | 60   | 64   | 68   | ms   |

| Standby Transition Time (at end of voice output) | t <sub>STB</sub>   | — (note)                                 | 200  | 250  | 300  | ms   |

| Silence Time Between Phrases                     | t <sub>BLN</sub>   | f <sub>SAM</sub> = 8 kHz (note)          | 350  | 375  | 500  | μs   |

(Note) Proportional to master the periods of oscillation frequencies  $f_{\text{OSC1}}$  and  $f_{\text{OSC2}}$ . The rated values show values when the standard master oscillation frequency is used.

## TIMING DIAGRAMS

#### **AC Characteristics at Power-On**

## AC Characteristics in Standby Status and when the IC is Activated

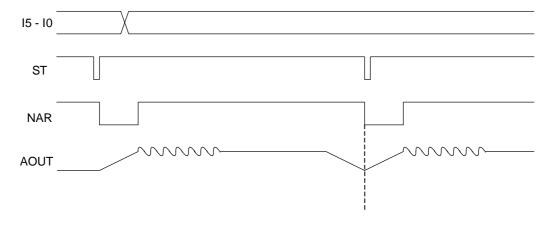

## **Playback Timing**

#### **FUNCTIONAL DESCRIPTION**

000001

111111

#### 1. Playback Code Specification

The user can specify a maximum of 63 phrases. Table 1.1 shows the settings by the I5-I0 pins.

I5-I0

Code Details

000000

Stop code

User-specified phrase (63 Phrases)

Table 1.1 User-specified Phrases

#### 2. Address Data

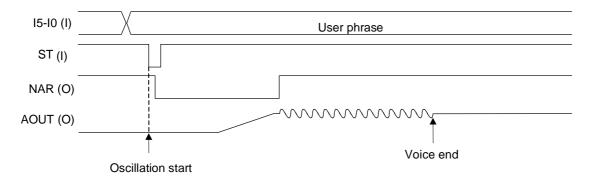

If a phrase is input at I5-I0 pins by address data, and if a ST pulse is then applied, voice playback starts. Figure 2.1 shows voice start timing. Figure 2.2 shows timing when an address other than a phrase is input.

Figure 2.1 Voice Start Timing

Figure 2.2 Timing when Address Other than a Phrase is Input in Stand-by Mode

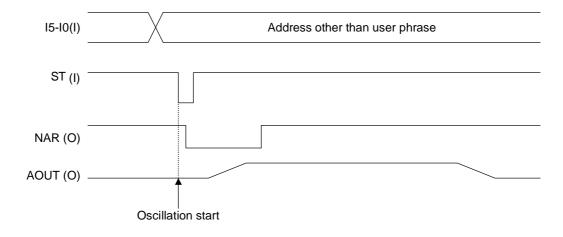

#### 3. Stop Code

If I5-I0 are set to "000000" during voice playback, and a ST signal is input, playback stops regardless of whether NAR is at "H" or "L" level, then AOUT becomes  $1/2 I_{AOUT}$ . Stop code becomes valid at the falling edge of ST.

Figure 3.1 shows stop code input timing.

Figure 3.1 Stop Code Input Timing

The stop code does not initialize internal units but only stops playback. To initialize an internal register, use the RESET pin.

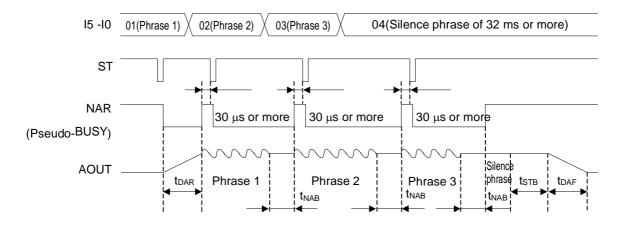

#### 4. Generating Pseudo-BUSY Signal through NAR Pin

If the application in use requires a BUSY signal when this IC is used in microcontroller interface mode, a pseudo-BUSY signal can be generated through the NAR pin by controlling signal timing, as shown below.

When edit ROM is not used

When edit ROM is used

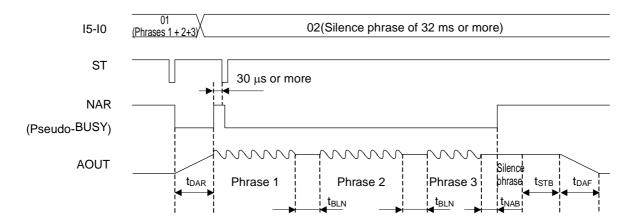

## APPLICATION CIRCUIT

**Application Circuit in Microcontroller Interface**

#### (3) COMMON

#### **Sampling Frequency**

As shown in Table 1.1, 7 sampling frequencies are available. A sampling frequency can be selected and assigned to each phrase in ROM data.

**Table 1.1 Sampling Frequency**

| Sampling Fraguency                                      | Frequency diving ratio  |                       |  |  |

|---------------------------------------------------------|-------------------------|-----------------------|--|--|

| Sampling Frequency  (At standard assillation frequency) | XT/CR = "H"             | XT/CR = "L"           |  |  |

| (At standard oscillation frequency)                     | Ceramic Oscillation     | CR Oscillation        |  |  |

| 4.0 kHz                                                 | f <sub>OSC1</sub> /1024 | f <sub>OSC2</sub> /64 |  |  |

| 5.3 kHz                                                 | f <sub>OSC1</sub> /768  | f <sub>OSC2</sub> /48 |  |  |

| 6.4 kHz                                                 | f <sub>OSC1</sub> /640  | f <sub>OSC2</sub> /40 |  |  |

| 8.0 kHz                                                 | f <sub>OSC1</sub> /512  | f <sub>OSC2</sub> /32 |  |  |

| 10.6 kHz                                                | f <sub>OSC1</sub> /384  | Unavailable           |  |  |

| 12.8 kHz                                                | f <sub>OSC1</sub> /320  | Unavailable           |  |  |

| 16.0 kHz                                                | f <sub>OSC1</sub> /256  | Unavailable           |  |  |

Note: When CR oscillation is selected, 10.6 kHz, 12.8 kHz, and 16 kHz cannot be selected.

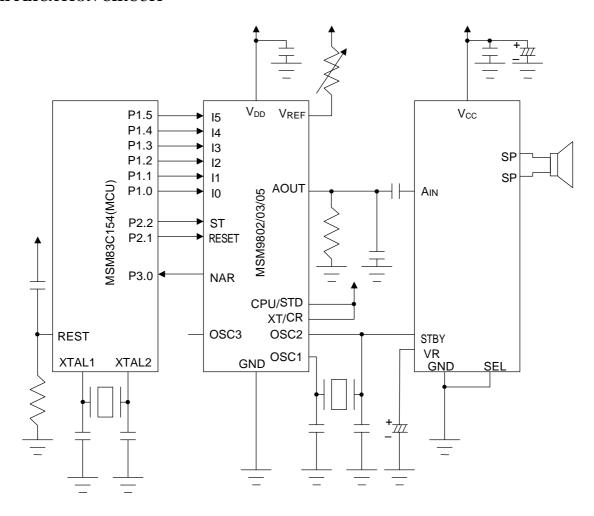

#### Recording/Playback Time

Figure 2.1 below shows memory allocation of the on-chip Mask ROM. About 11 Kbits of data area is allocated for the Phrase Control Table, Phrase Data Control and Test Data.

Therefore, actual data area for storing sound data equals the total Mask ROM capacity minus 11 Kbits.

Figure 2.1 Memory Allocation of On-chip Mask ROM

The playback time is obtained by dividing the memory capacity by the bit rate. The playback time for 8-bit PCM algorithm is obtained by using the following equation.

Playback time [sec] =

$$\frac{\text{Memory capacity [bit]}}{\text{Bit rate [bps]}} = \frac{\text{Memory capacity [bit]}}{\text{Sampling frequency [Hz]} \times 8 \text{ [bit]}}$$

For example, if all phrases are stored in the MSM9802 at 8 kHz sampling frequency, the maximum playback time is as follows.

Playback time =

$$\frac{(512-11) \times 1024 \text{ [bit]}}{8000 \text{ [Hz]} \times 8 \text{ [bit]}} \approx 8.0 \text{ [sec]}$$

Table 2.1 Maximum playback time

| Model   | POM consoity | Lloorio orog | Maximum playback time (sec) |                             |                             |                              |  |  |

|---------|--------------|--------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|--|--|

| Model   | ROM capacity | User's area  | $f_{SAM} = 4.0 \text{ kHz}$ | $f_{SAM} = 6.4 \text{ kHz}$ | $f_{SAM} = 8.0 \text{ kHz}$ | $f_{SAM} = 16.0 \text{ kHz}$ |  |  |

| MSM9802 | 512K bit     | 501K bit     | 16.0                        | 10.0                        | 8.0                         | 4.0                          |  |  |

| MSM9803 | 1M bit       | 1013K bit    | 32.4                        | 20.2                        | 16.2                        | 8.1                          |  |  |

| MSM9805 | 2M bit       | 2037K bit    | 65.1                        | 40.7                        | 32.5                        | 16.2                         |  |  |

#### **Playback Method**

This IC provides two kinds of playback methods, non-linear PCM algorithm and straight PCM algorithm. When the 8-bit non-linear PCM algorithm is selected, sound quality can be improved because a resolution equivalent to 10-bit straight PCM is available around the waveform center. You can select either non-linear PCM algorithm or straight PCM algorithm for each phrase. Table 3.1 shows the relationship between playback methods and applicable sounds. It is recommended to evaluate the sound quality before actual use.

Table 3.1 Relationship between playback methods and applicable sounds

| Playback method                | Applicable sound         |

|--------------------------------|--------------------------|

| 8-bit non-linear PCM algorithm | Human voice              |

| 8-bit straight PCM algorithm   | BEEP tone, sound effects |

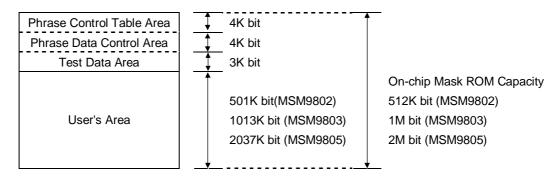

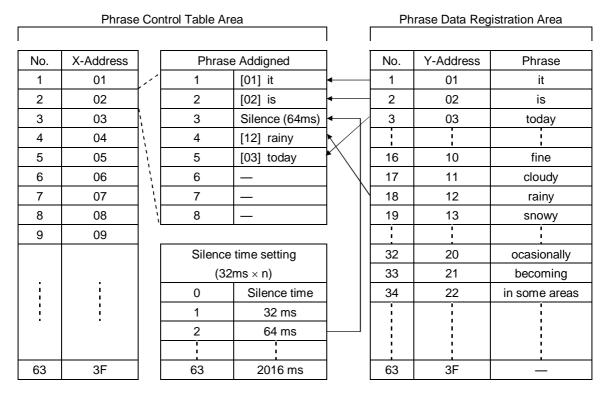

#### **Phrase Control Table**

Because the LSI contains the Phrase Control Table, it is possible to play back multiple phrases in succession by a single easy control operation like controlling a single regular phrase playback. Up to 8 combined phrases including a silence can be registered in a single address in the Phrase Control Table.

Further, you can use the maximum memory space for data storage because it is not required to have the same phrase data.

To show an example, let's assume that your application needs to speak two similar sentences, "It is fine today" and "It is rainy today." The two sentences have the common words "it", "is" and "today". What you have to do is to prepare these common sound data, not in sentences but in words, and to store each combined phrase data in Phrase Control Table as shown in Table 4.1 and Figure 4.1

Multiple phrases can be played continuously merely by specifying a desired phrase using an X address. For an example from Table 4.1, when address "01" is specified, "It is fine today" is played, and when address "02" is specified, "It is rainy" is played.

Phrase Control Table, a silence can be inserted without using the User's Area.

Minimum time for silence 32 ms

Maximum time for silence 2016 ms

Time unit for setting up silence 32 ms

Table 4.1 Matrix of the Phrase Control Table

| No. | X-Address<br>(HEX) |      |      | (1      | Sound Data |        |        |        |      |                                                        |

|-----|--------------------|------|------|---------|------------|--------|--------|--------|------|--------------------------------------------------------|

| 1   | 01                 | [01] | [02] | Silence | [10]       | [03]   | !<br>! | !<br>! |      | It is (silence) fine today.                            |

| 2   | 02                 | [01] | [02] | Silence | [12]       | [03]   | !<br>! | !<br>! |      | It is (silence) rainy today.                           |

| 3   | 03                 | [01] | [02] | [10]    | [21]       | [11]   | [12]   | [22]   | [03] | It is fine becoming cloudy, rainy in some areas today. |

|     |                    |      |      |         | !          | !<br>! | !      | !<br>! |      |                                                        |

| 62  | 3E                 |      |      |         | !<br>!     | i<br>I | !<br>! | <br>   |      |                                                        |

| 63  | 3F                 |      |      |         | i<br>I     | i<br>I | i<br>I | i<br>I |      |                                                        |

Figure 4.1 Phrase Combination Matrix for Phrase Control Table

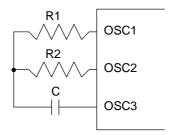

## **CR** Oscillation

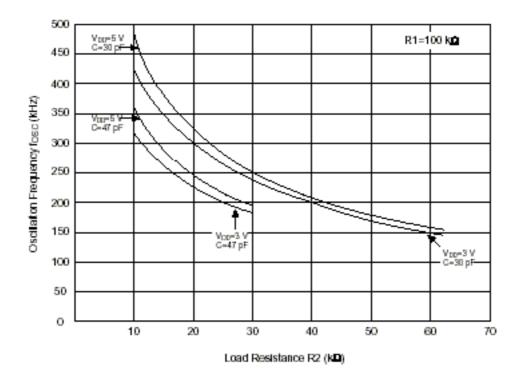

Figure 5.1 shows an external circuit using CR oscillation. Figure 5.2 shows the CR oscillation frequency characteristics.

Figure 5.1 CR Oscillation

Figure 5.2 CR Oscillation Frequency Characteristics

#### **Determining CR constants**

The CR oscillation frequency characteristics are shown in Figure 5.2. If  $f_{osc}$  is set to 256 kHz, use the following values as a guide (see Figure 5.2) to set the C and R2 that fit the printed-circuit board type used.

$$R1 = 100 \text{ k}\Omega, R2 = 30 \text{ k}\Omega, C = 30 \text{ pF}$$

When choosing CR oscillation, the CR oscillation frequency varies according to the fluctuation of the external C and R2.

Fluctuation of CR oscillation frequencies

When choosing CR oscillation, the error of CR oscillation frequency due to process variations of the IC is  $\pm$  4% maximum, and the fluctuation of the CR oscillation frequency when using a capacitor (C) of  $\pm$  1% accuracy and a resistor (R2) of  $\pm$  2% accuracy is a maximum of  $\pm$  7% approximately.

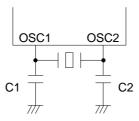

#### **Ceramic Oscillation**

Figure 6.1 shows an external circuit using a ceramic oscillator.

Figure 6.1 Ceramic Oscillation Diagram

For example, the following table shows the optimum load capacitances, power supply voltage ranges, and operating temperature ranges when ceramic oscillators made by Murata MFG Co., Ltd., Kyocera Co., Ltd. and TDK Co., Ltd. are used.

|               | Ceramic oscillator |                    | Optimal load capacity |           | Supply voltage | Operating temperature range |  |

|---------------|--------------------|--------------------|-----------------------|-----------|----------------|-----------------------------|--|

| Maker         | Туре               | Frequency<br>(MHz) | C1 (pF)               | C2 (pF)   | range (V)      | (°C)                        |  |

| Iţa           | CSTCR4M09G53-R0    |                    |                       |           | 2.3 to 5.5     | -40 to +85                  |  |

| Murata<br>MFG | CSTLS4M09G53-B0    | 4.096              | Built in              | Built in  | 2.4 to 5.5     |                             |  |

|               | PBRC4.00A          |                    | 33 Built in           | 33        |                | -20 to +80                  |  |

| Kyocera       | KBR-4.0MSB         | 4.0                |                       |           | 3.1 to 5.5     |                             |  |

| Š             | PBRC4.00B          | 4.0                |                       | Built in  | 3.1 10 3.5     | -20 10 +60                  |  |

|               | KBR-4.0MKC         |                    | Duilt III             | Duilt iii |                |                             |  |

| TDK           | CCR4.00MC3         | 4.0                | Built in              | Built in  | 2.4 to 5.5     | -40 to +85                  |  |

(Note) When a 4 MHz ceramic oscillator is used, the playback speed of MSM9802/03/05 is slower by 2 percent than that of an analysis tool or a demonstration board.

## **Low-Pass Filter**

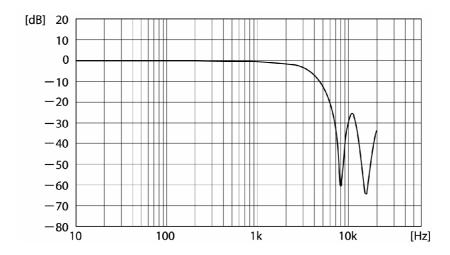

In this IC, all voice outputs are through the built-in low-pass filter (LPF). Figure 7.1 and Table 7.2 show the LPF frequency characteristics and LPF cutoff frequency respectively. Only the voice output through LPF is enabled in this IC.

Figure. 7.1 LPF Frequency Characteristics (f<sub>SAM</sub> = 8 kHz)

**Table 7.2 LPF Cutoff Frequency**

| Sampling Frequency (kHz) | Cutoff Frequency (kHz) |  |  |  |

|--------------------------|------------------------|--|--|--|

| (f <sub>SAM</sub> )      | (f <sub>cut</sub> )    |  |  |  |

| 4.0                      | 1.2                    |  |  |  |

| 5.3                      | 1.6                    |  |  |  |

| 6.4                      | 2.0                    |  |  |  |

| 8.0                      | 2.5                    |  |  |  |

| 10.6                     | 3.2                    |  |  |  |

| 12.8                     | 4.0                    |  |  |  |

| 16.0                     | 5.0                    |  |  |  |

#### **Standby Transition**

When playback of a phrase is finished, if playback of the next phrase does not start up within  $t_{STB}$  (0.25 sec. typ.), the IC enters standby status and the entire operation stops.

Figure 8.1 Timing for Voice Playback during D/A Converter Change Time (Stand-alone Mode)

Figure 8.2 Timing for Voice Playback during D/A Converter Change Time (Microcontroller Interface Mode)

If playback is attempted during D/A converter change time as shown in figures 8.1 and 8.2, the IC exits from standby status and the output from the D/A converter begins going to the  $1/2~I_{AOUT}$  level. When the output reaches  $1/2~I_{AOUT}$ , voice playback starts.

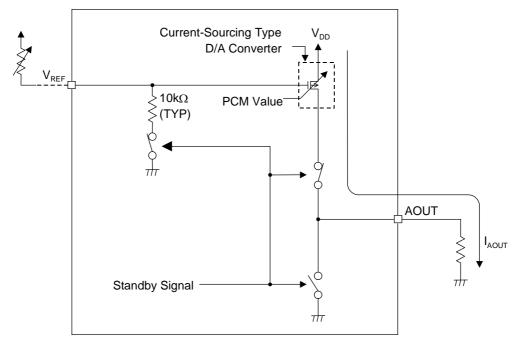

# **Voice Output Unit Equivalent Circuit (AOUT, FREF Pins)**

(The above switch positions show those when the circuit is active.)

Figure 9.1 Voice Output Unit Equivalent Circuit

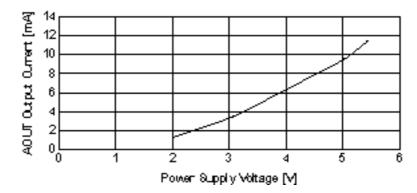

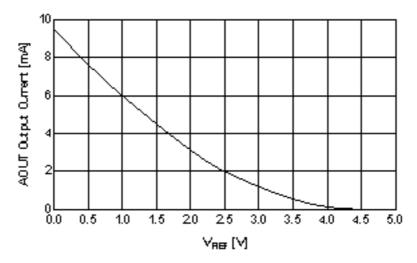

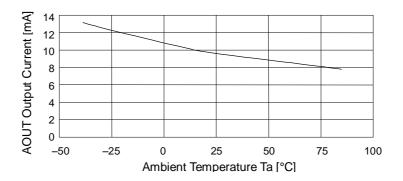

## D/A CONVERTER OUTPUT CURRENT CHARACTERISTICS

Power Supply Voltage vs. Output Current Characteristics (Ta = 25°C, V<sub>AOUT</sub> = 0V)

Temperature vs. Output Current Characteristics ( $V_{DD} = 5V$ ,  $V_{AOUT} = 0V$ )

$V_{REF}$  Voltage vs. Output Current Characteristics (Ta = 25°C,  $V_{DD}$  = 5V,  $V_{AOUT}$  = 0V)

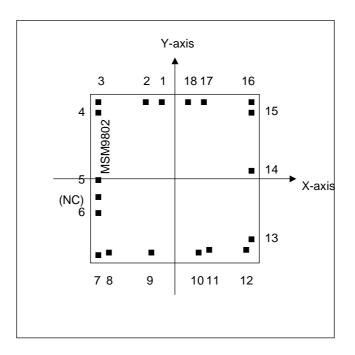

## **PAD CONFIGURATION**

#### MSM9802

## **Pad Layout**

Chip size : X = 3.22mm Y = 3.17mm

Chip thickness :  $350 \mu m \pm 30 \mu m$ Pad size :  $110 \mu m \times 110 \mu m$

Substrate potential : GND

## **Pad Coordinates**

(Chip center is located at X = 0 and Y = 0)

| (Unit: µ | um) |

|----------|-----|

|----------|-----|

|         |           |                  |        |         |          |        | (Orne: pini) |

|---------|-----------|------------------|--------|---------|----------|--------|--------------|

| Pad No. | Pad Name  | X-axis           | Y-axis | Pad No. | Pad Name | X-axis | Y-axis       |

| 1       | I3/ (A0)  | <del>-4</del> 15 | 1385   | 10      | VDD      | 462    | -1347        |

| 2       | I4/ (A1)  | -816             | 1385   | 11      | OSC1     | 742    | -1333        |

| 3       | I5/ (A2)  | -1460            | 1385   | 12      | OSC2     | 1349   | -1333        |

| 4       | RESET     | -1460            | 1049   | 13      | OSC3     | 1460   | -972         |

| 5       | XT/CR     | -1458            | -20    | 14      | CPU/STD  | 1389   | 183          |

| 6       | NAR       | -1460            | -899   | 15      | ST/(RND) | 1389   | 1058         |

| 7       | GND       | -1460            | -1375  | 16      | 10/(SW0) | 1389   | 1385         |

| 8       | $V_{REF}$ | -1135            | -1333  | 17      | I1/(SW1) | 719    | 1385         |

| 9       | AOUT      | <b>-</b> 585     | -1333  | 18      | 12/(SW2) | 276    | 1385         |

Pad name in parentheses is for stand-alone mode.

## MSM9803

#### **Pad Layout**

Chip size : X = 3.22mm Y = 4.06mm

Chip thickness :  $350\mu m \pm 30\mu m$ Pad size :  $110\mu m \times 110\mu m$

Substrate potential : GND

## **Pad Coordinates**

(Chip center is located at X = 0 and Y = 0)

|         |           |                  |        |         |          |        | (Unit: µm) |

|---------|-----------|------------------|--------|---------|----------|--------|------------|

| Pad No. | Pad Name  | X-axis           | Y-axis | Pad No. | Pad Name | X-axis | Y-axis     |

| 1       | I3/ (A0)  | <del>-4</del> 15 | 1829   | 10      | VDD      | 452    | -1788      |

| 2       | I4/ (A1)  | -816             | 1829   | 11      | OSC1     | 742    | -1776      |

| 3       | I5/ (A2)  | -1460            | 1829   | 12      | OSC2     | 1349   | -1776      |

| 4       | RESET     | -1460            | 1493   | 13      | OSC3     | 1460   | -1415      |

| 5       | XT/CR     | -1458            | 424    | 14      | CPU/STD  | 1389   | 628        |

| 6       | NAR       | -1460            | -1342  | 15      | ST/(RND) | 1389   | 1502       |

| 7       | GND       | -1460            | -1818  | 16      | 10/(SW0) | 1389   | 1829       |

| 8       | $V_{REF}$ | -1135            | -1776  | 17      | I1/(SW1) | 720    | 1829       |

| 9       | AOUT      | -585             | -1776  | 18      | 12/(SW2) | 276    | 1829       |

Pad name in parentheses is for stand-alone mode.

## MSM9805

#### **Pad Layout**

Chip size : X = 3.22mm Y = 5.96mm

$\begin{array}{lll} \text{Chip thickness} & : & 350 \mu\text{m} \pm 30 \mu\text{m} \\ \text{Pad size} & : & 110 \mu\text{m} \times 110 \mu\text{m} \end{array}$

Substrate potential : GND

#### **Pad Coordinates**

(Chip center is located at X = 0 and Y = 0)

| . 1     |          |                  | ,      |         |          |        | (Unit: µm) |

|---------|----------|------------------|--------|---------|----------|--------|------------|

| Pad No. | Pad Name | X-axis           | Y-axis | Pad No. | Pad Name | X-axis | Y-axis     |

| 1       | I3/ (A0) | <del>-4</del> 15 | 2777   | 10      | VDD      | 452    | -2723      |

| 2       | I4/ (A1) | -816             | 2777   | 11      | OSC      | 742    | -2726      |

| 3       | I5/ (A2) | -1460            | 2777   | 12      | OSC2     | 1349   | -2726      |

| 4       | RESET    | -1460            | 882    | 13      | OSC3     | 1460   | -1532      |

| 5       | XT/CR    | -1458            | 364    | 14      | CPU/STD  | 1453   | 267        |

| 6       | NAR      | -1460            | -1546  | 15      | ST/(RND) | 1455   | 1338       |

| 7       | GND      | -1460            | -2768  | 16      | 10/(SW0) | 1432   | 2777       |

| 8       | VREF     | -1136            | -2726  | 17      | I1/(SW1) | 754    | 2777       |

| 9       | AOUT     | -585             | -2726  | 18      | 12/(SW2) | 312    | 2777       |

Pad name in parentheses is for stand-alone mode.

#### PACKAGE DIMENSIONS

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

|                   |               | Page                |                    |                                                                                                                                                                                   |  |

|-------------------|---------------|---------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Document No.      | Date          | Previous<br>Edition | Current<br>Edition | Description                                                                                                                                                                       |  |

| FEDL9802-03-05-04 | Nov. 2001     | _                   | -                  | Final edition 4                                                                                                                                                                   |  |

| FEDL9802-03-05-05 | Nov. 4, 2003  | 33                  | 33                 | The pulse widths of the pseudo BUSY signals (through the NAR Pin) when edit ROM is not used and when edit ROM is used have been changed from 30 ms or more to 30 $\mu s$ or more. |  |

| FEDL9802-03-05-06 | Nov. 22, 2005 | 34                  | 34                 | The AMP name was deleted in application circuit.                                                                                                                                  |  |

#### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by Oki, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

- Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2005 Oki Electric Industry Co., Ltd.